# MICROPROCESSOR INTERFACING

BY JOSEPH J. CARR

# MICROPROCESSOR INTERFACING

BY JOSEPH J. CARR

#### FIRST EDITION

#### **FIRST PRINTING**

Copyright  ${\hbox{$\mathbb C$}}$  1982 by TAB BOOKS Inc.

Printed in the United States of America

Reproduction or publication of the content in any manner, without express permission of the publisher, is prohibited. No liability is assumed with respect to the use of the information herein.

Library of Congress Cataloging in Publication Data

Carr, Joseph J.

Microprocessor interfacing

Microprocessor interfacing.

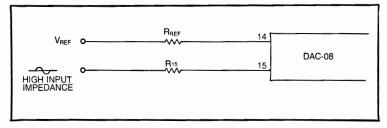

Includes index.

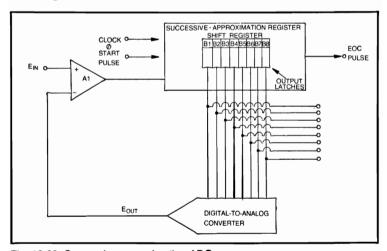

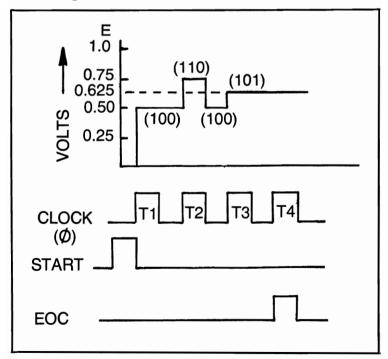

1. Microprocessors. 2. Interface circuits.

I. Title.

TK7895.M5C37 001.64 81-18282

ISBN 0-8306-0064-7 AACR2 ISBN 0-8306-1396-X (pbk.)

# **Contents**

|   | Introduction                                                                                                                                                                                                                                                                                                              | ٧  |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1 | Introduction to Digital Electronics Logic States—Positive and Negative Logic—Logic Families— Speed Versus Power—RTL Devices—DTL Devices—TTL Devices—CMOS Devices—HTL Devices—Emitter-Coupled Logic—Gates—TTL and CMOS Examples—Flip-Flops— Additional Types of Flip-Flops—Multivibrators—Shift Registers—Digital Counters | 1  |

| 2 | Interfacing Digital IC Families                                                                                                                                                                                                                                                                                           | 39 |

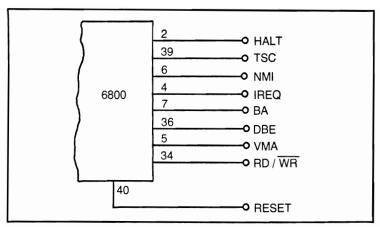

| 3 | Control Signals Z-80 Control Signals—8080A Control Signals—6502 Control Signals—6800 Control Signals                                                                                                                                                                                                                      | 42 |

| 4 | Address Decoder and Device Select Circuits  Addressing in Microcomputers—Eight-Bit Decoders—Address-Block Decoding—Generating Port /Device Select Signals                                                                                                                                                                 | 47 |

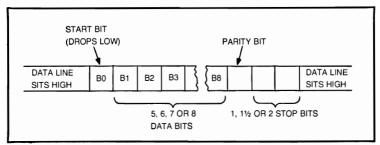

| 5 | I/O Interfacing I/O Ports—Parallel-Outport Port-Design—Parallel-Input Port-Design—Bidirectional Parallel-I/O Port-Design—Serial I/O-Ports—Software Serial-I/O-Ports—TTL /CMOS Hardware Methods—RS-232 Interfacing—Current-Loop Ports                                                                                      | 59 |

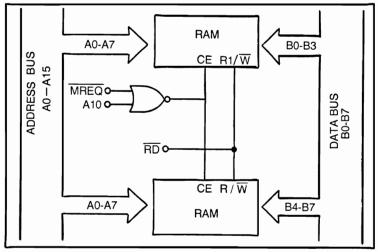

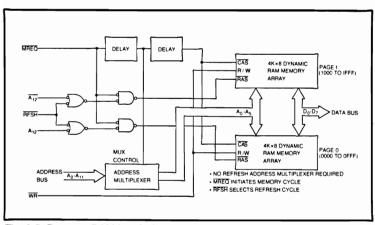

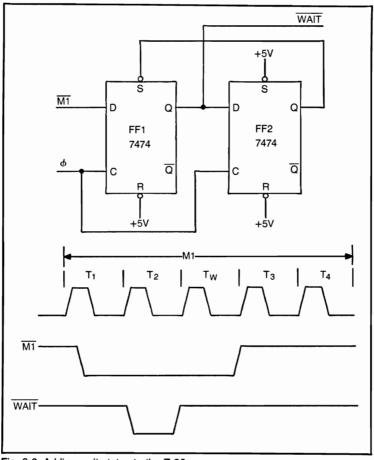

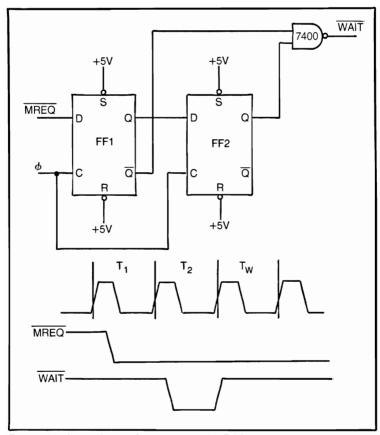

| 6 | <b>Memory Interfacing</b> Dynamic Memory—Adding Wait States—Memory-Mapped Devices                                                                                                                                                                                                                                         | 69 |

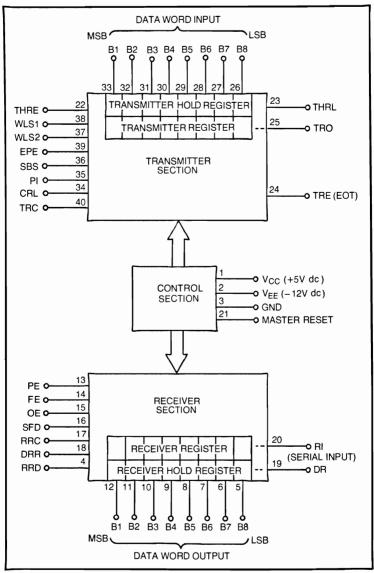

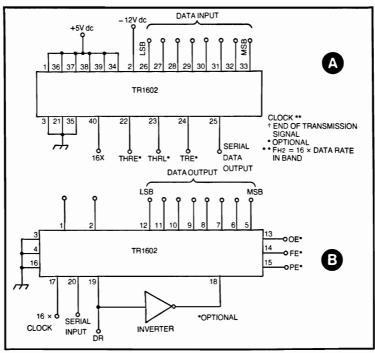

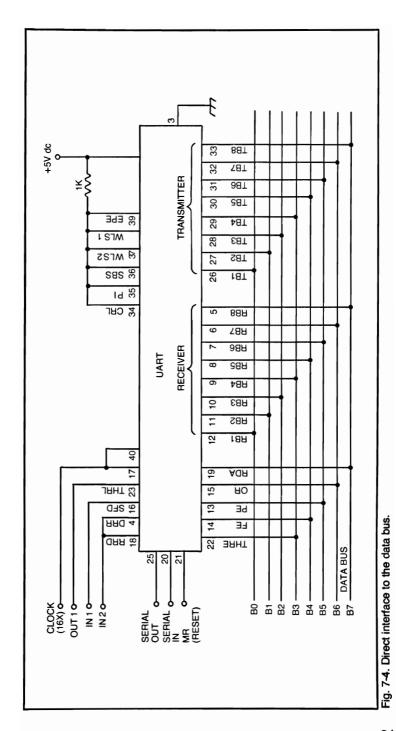

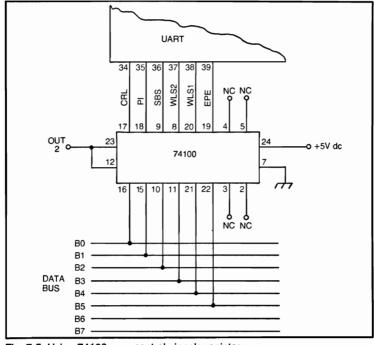

| 7 | UART                                                                                                                                                                                                                                                                                                                      | 77 |

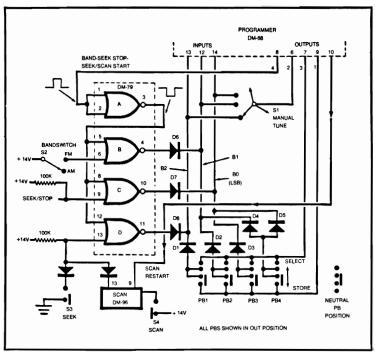

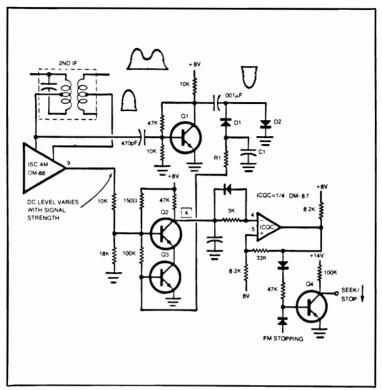

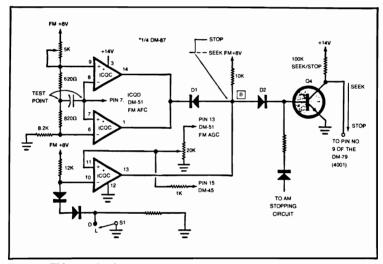

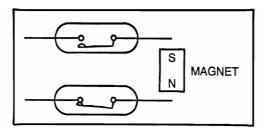

| 8  | Interfacing Keyboards, Push-buttons, and Sensors Digital Car-Radio Tuner—Seek and Scan Functions— Switches—Interfacing Switches—Keyboard Interfacing—Pulse Stretcher—Using the 555                                                                                          | 85  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

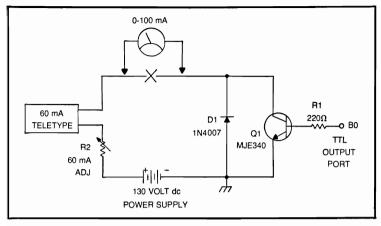

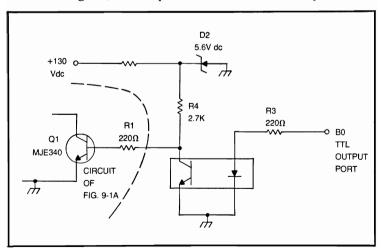

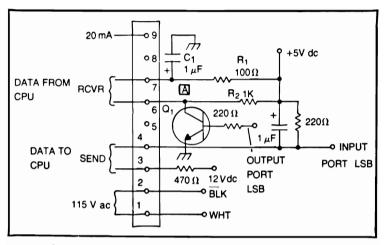

| 9  | Interfacing Printers and Teletypewriters                                                                                                                                                                                                                                    | 106 |

| 10 | Single-Board Computers                                                                                                                                                                                                                                                      | 111 |

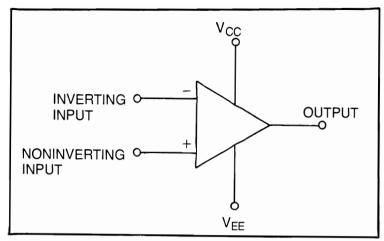

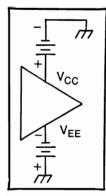

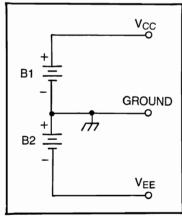

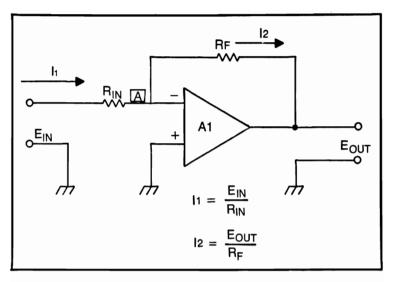

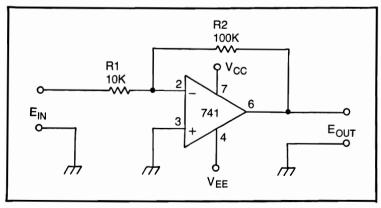

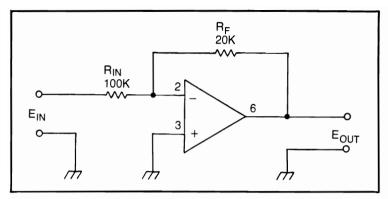

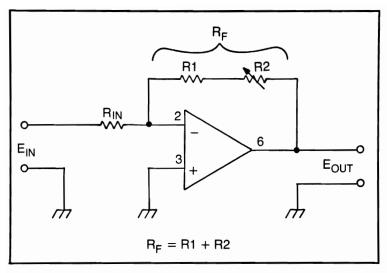

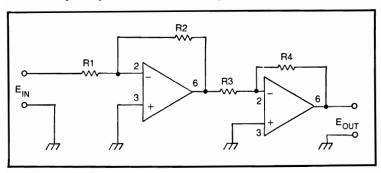

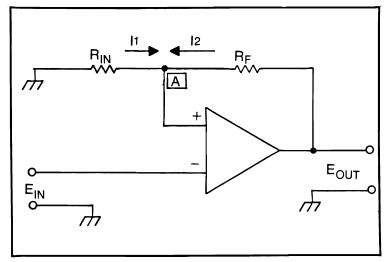

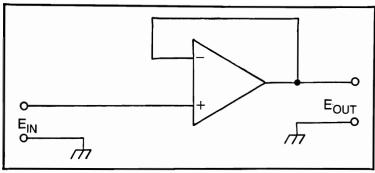

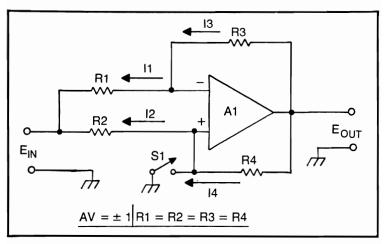

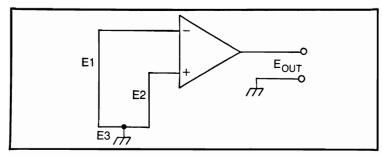

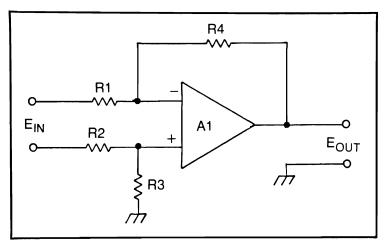

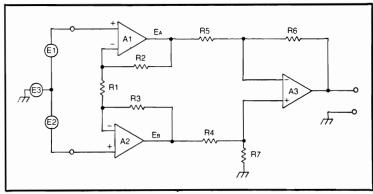

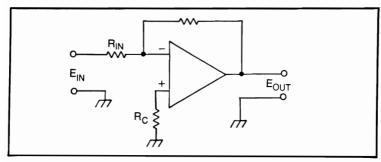

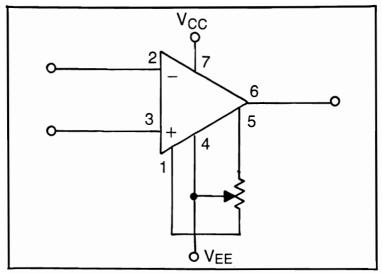

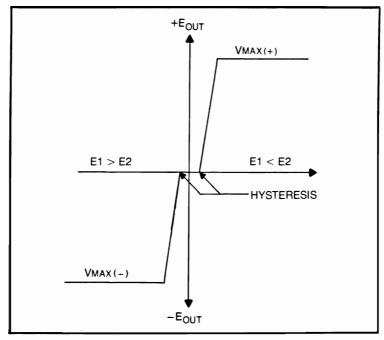

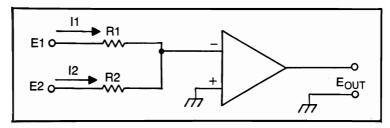

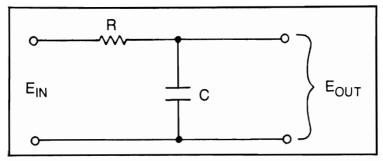

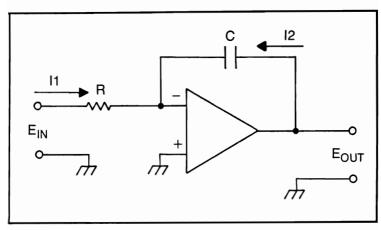

| 11 | Operational Amplifiers Ideal Operational-Amplifiers—Inverting Followers—Noninverting Followers—Positive-Negative Amplifier-Circuit—Differential Amplifiers—Operational-Amplifier Problems—Special Operational-Amplifier Circuits                                            | 113 |

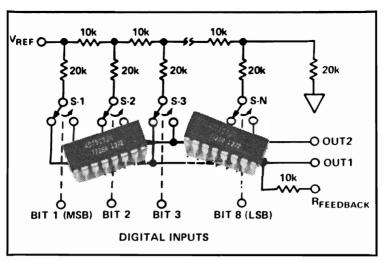

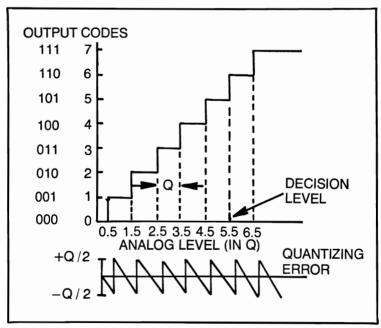

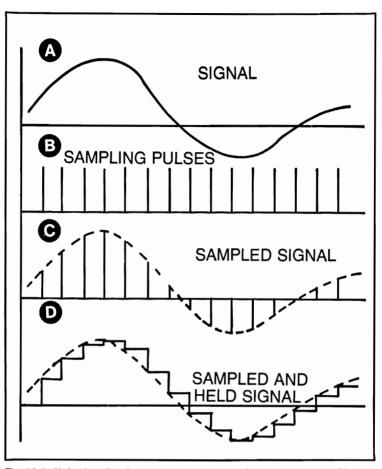

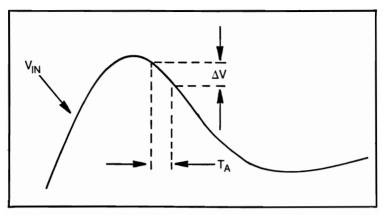

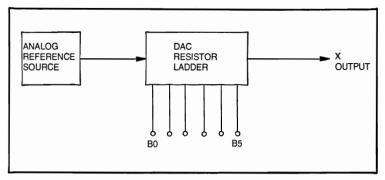

| 12 | Basics of Data Conversion Coding Schemes for Data Converters—Specifications—Digital-to-Analog Converters—Full-Scale Output Voltage—Amplifier Settling-Time—Analog-to-Digital Converters                                                                                     | 135 |

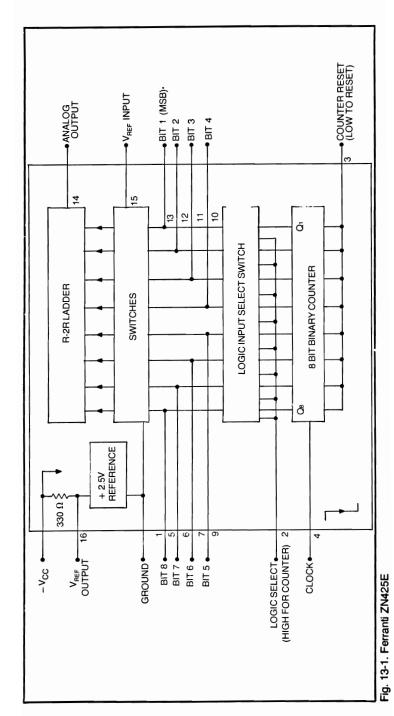

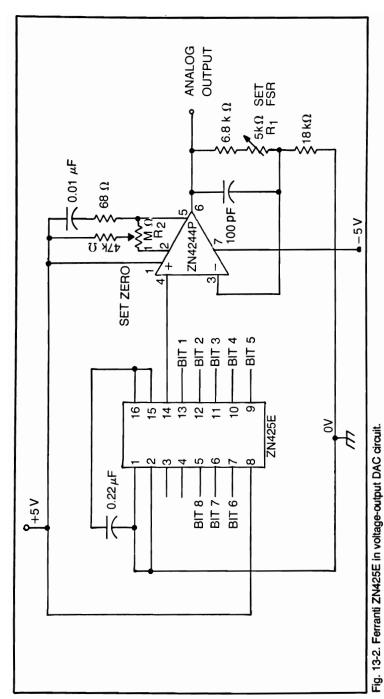

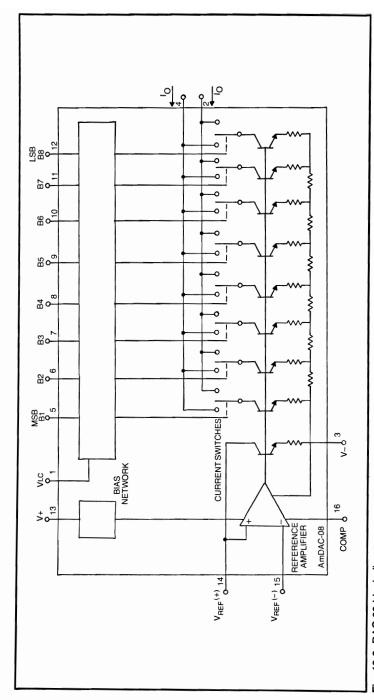

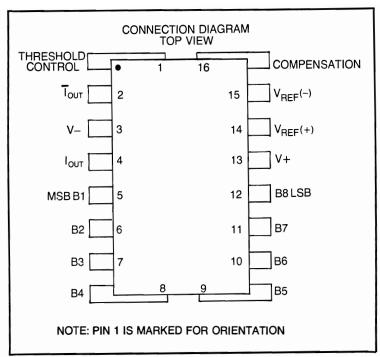

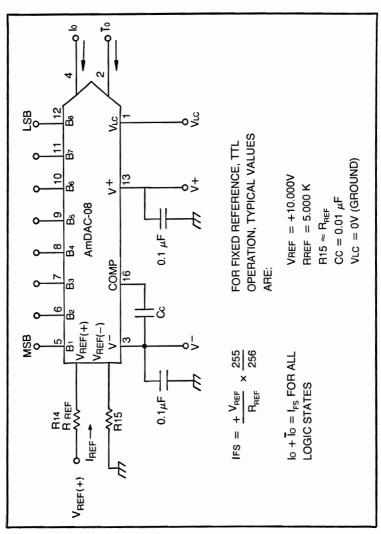

| 13 | Practical Digital-to-Analog Converters Ferranti ZN425E—PMI DAC-08                                                                                                                                                                                                           | 170 |

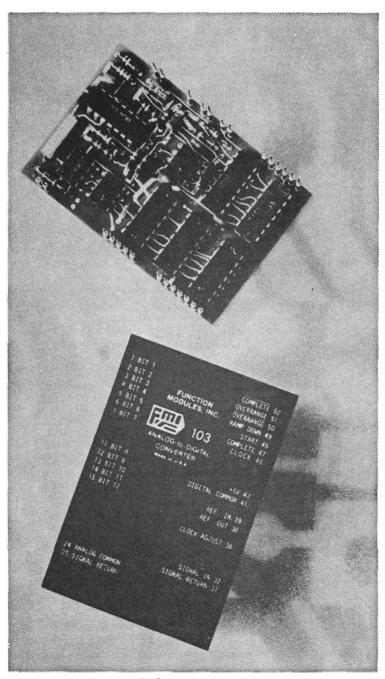

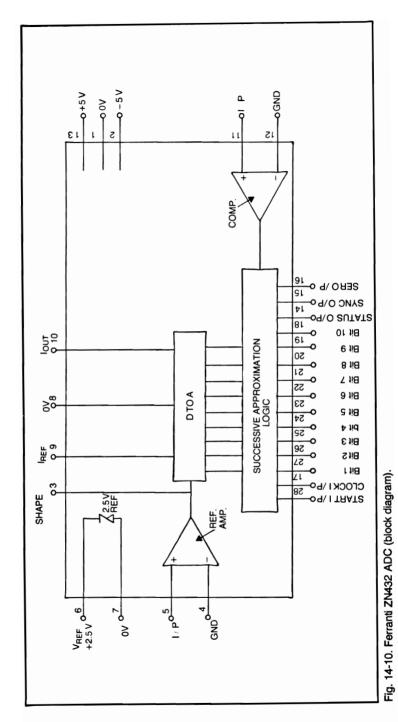

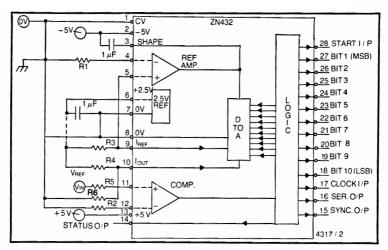

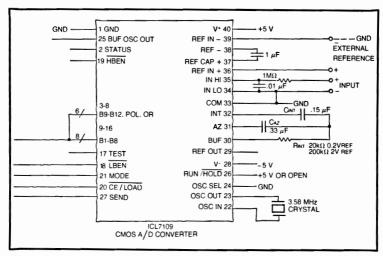

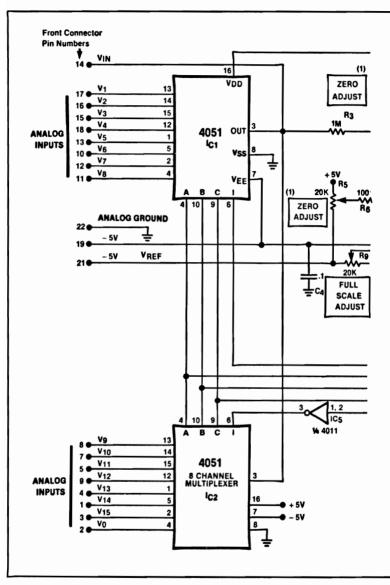

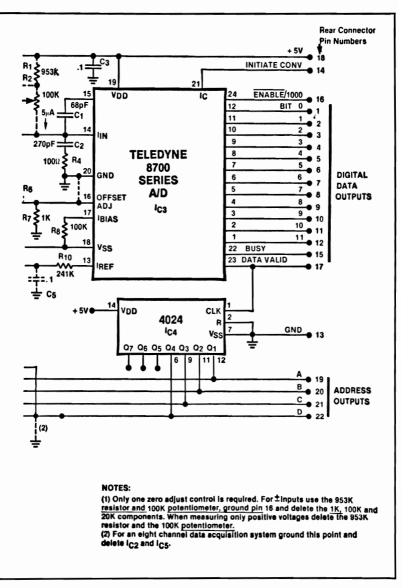

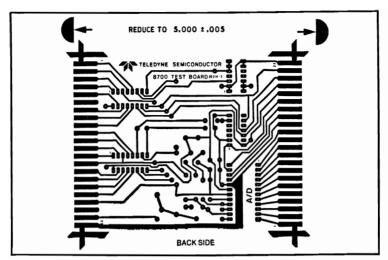

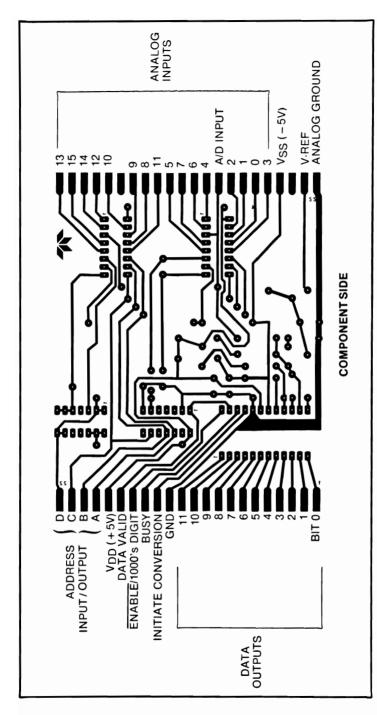

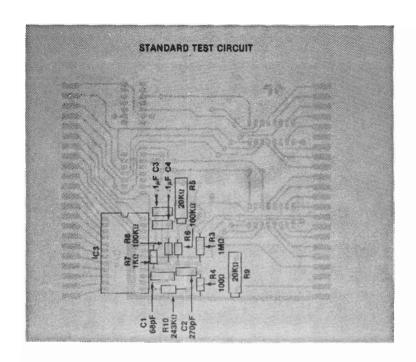

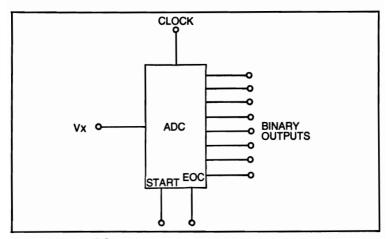

| 14 | Practical Analog-to-Digital Converters  Eight-Bit Binary Analog-to-Digital Converter—Eight-Bit Binary  Ramp ADC—Successive Approximation In Analog to Analog  Converters—Ferranti ZN432—Intersil ISL7109 12-Bit Binary  ADC—Teledyne 8700—Analog Devices AD7570—Hybrid ADCs | 186 |

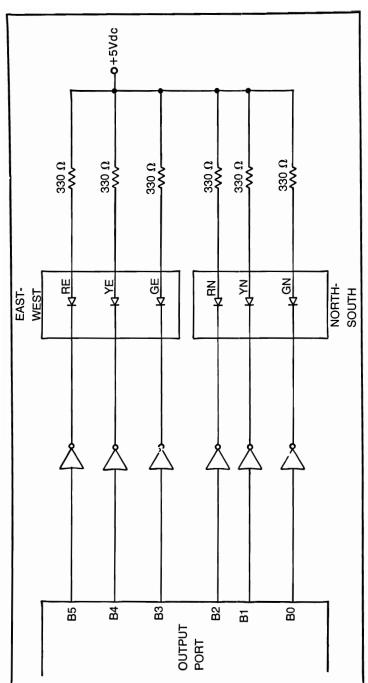

| 15 | Interfacing Motors, Triacs, and Relays  Motor Control—Controlling External Loads with Relays— Controlling a Triac or SCR with the Microcomputer—Traffic-Light Controller-An Exercise                                                                                        | 214 |

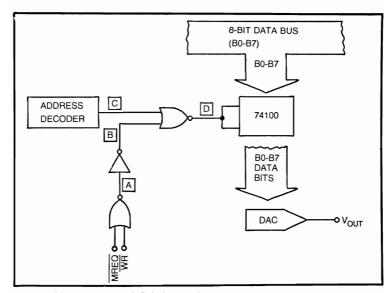

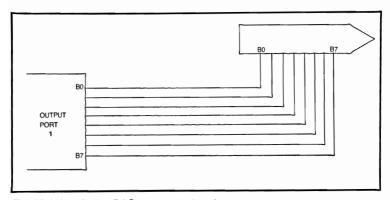

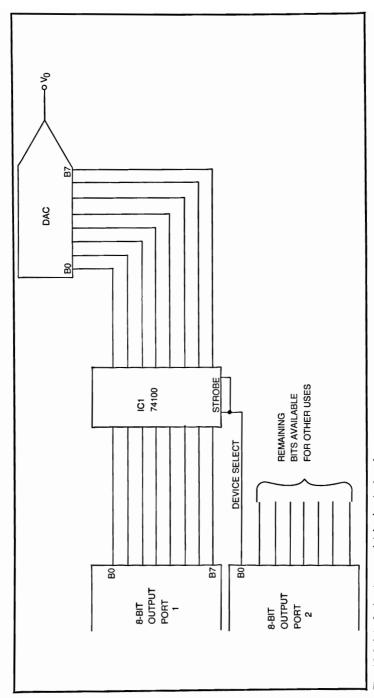

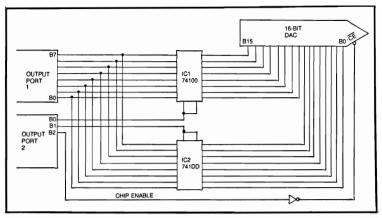

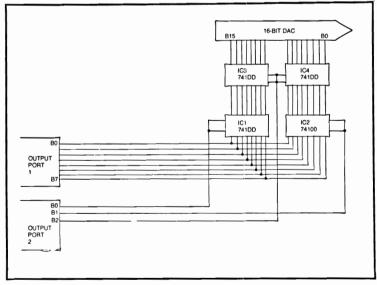

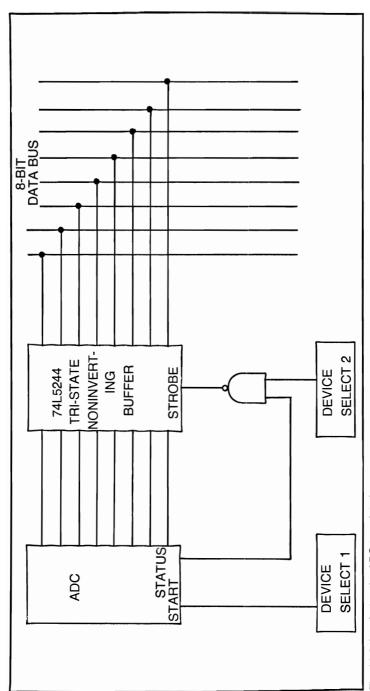

| 16 | Interfacing ADCs and DACs to the Microprocessor Interfacing DACs—Interfacing 10-, 12- and 16-Bit DACs to the 8-Bit Microcomputer—Interfacing the ADC to the Microprocessor                                                                                                  | 226 |

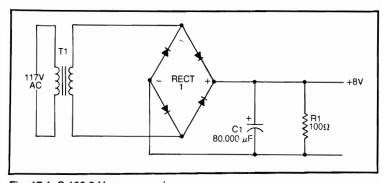

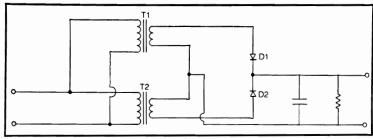

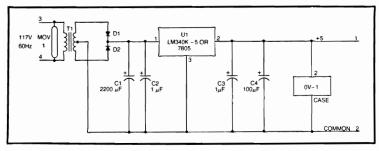

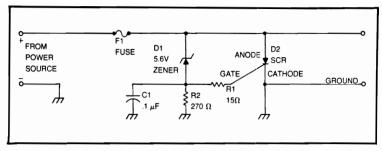

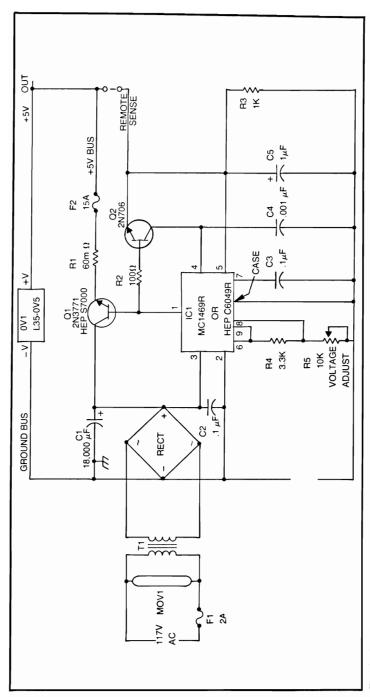

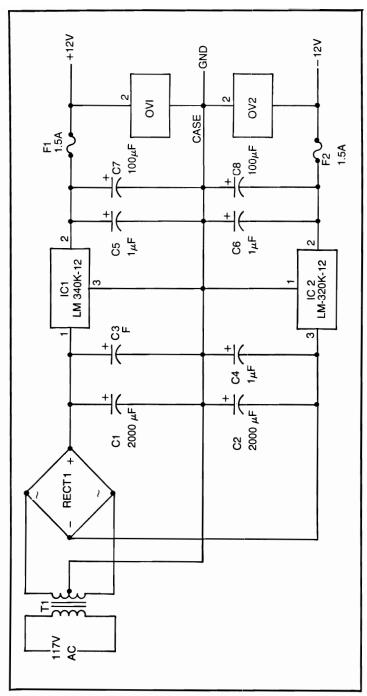

| 17 | DC Power Supplies S-100 Power Supply—+5-V Low Current Power Supply—5-V 10-A Power-Supply—±12-V 1-A Power-Supply                                                                                                                                                             | 237 |

|    | Index                                                                                                                                                                                                                                                                       | 246 |

### Introduction

The microcomputer age is not a decade old, but seldom has any one component or concept so rapidly revolutionized the electronics industry! Engineering schools can now advise students that an electrical engineer who is not conversant with microprocessor design methods will not remain employable for long! At first we were told that this situation would be true "in five years," but history has shown that two years was nearer the truth. Everything from children's toys to complicated scientific instruments onboard space ships has been computerized.

The proper application of the microprocessor/microcomputer requires a person who is a synergism of the software and hardware people found on larger systems. With "dinosaur" computers there are completely separate engineering and programming functions—carried out by different people; but on the microcomputer level when you treat the microprocessor or microcomputer as a component in an instrument design, you as the designer must be good at both.

This book will bring you quickly up to date on the elements of hardware interface with microprocessors. Covered in this volume are methods for interfacing memory devices, creating I/O (input-output) ports, and interfacing with such devices as keyboards, printers, sensors, and the analog world.

# Chapter 1

## **Introduction to Digital Electronics**

Digital electronics is a general field that encompasses digital computers, including microcomputers. Before you try to solve microprocessor interfacing problems you must learn the basics of digital electronics. Whether or not you are professionally involved in electronics, you should learn this material because no one any longer can safely ignore the world of digital electronics. Even radio and television technicians find digital circuits in the products they repair. Computerized color-television tuning and stereo-FM tuning are almost the rule, rather than the high-priced exception.

Digital electronics is, however, often simpler than analog electronics because digital IC (integrated circuit) devices recognize only two states, i.e., on and off. This makes digital circuits similar to relays and switches. In fact some digital circuits are little more than high-frequency-electronics versions of simple switches. It is my opinion that anyone who can understand simple relay and switch-logic circuits can also understand digital electronics. Certainly anyone who can understand color television, SSB (single sideband), FM two-way radios, and certain other complex products can understand digital electronics.

#### **LOGIC STATES**

Digital circuits respond to only two different input states. These states are called 1 and 0 (after the two permissible digits of the *binary*, or base-2, number system), high and low, or (in older texts) true and false. These designations are merely representations of two different voltage states. In this book the high/low designation is used because it graphically describes what is happening to the circuit.

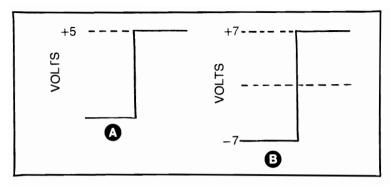

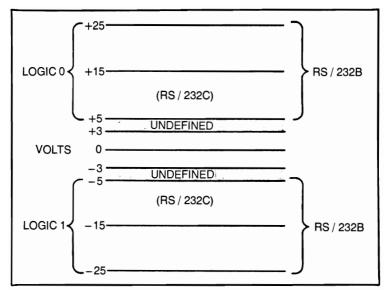

Transistor-transistor-logic (TTL) responds only to 0 and +5 V for the two logic levels. If any other voltage levels are used the TTL device either (1) fails to work, (2) works unpredictably, or (3) burns out. Figure 1-1A shows the TTL levels.

Complimentary metal-oxide semiconductor (CMOS) IC logic devices can use the same 0 and +5 V logic levels as the TTL devices but may also be

Fig. 1-1. (A) TTL logic levels and (B) CMOS logic levels.

used at any combination of voltage levels between  $\pm 4$  V and  $\pm 15$  V. In CMOS, illustrated in Fig. 1-1B,  $\pm 7$  V is used. The voltage levels that represent high and low conditions in CMOS need not be equal. In fact many circuits use a positive voltage (i.e., +12 V), and 0 V for high and low conditions, respectively. Some CMOS digital devices, notably complex function devices, fail to operate properly and predictably if the applied voltage is less than 7 V. These devices sometimes refuse to operate properly on TTL levels of 0 and +5 V despite claims to the contrary.

#### POSITIVE AND NEGATIVE LOGIC

You may sometimes hear the terms positive and negative logic. These terms tend to confuse the newcomer and mean nothing more than how the high and low logic states are related to voltage levels. In *positive logic* the high is logical-1 and is a positive voltage (i.e., +5 V in the case of TTL). The low, logical-0, is 0 V in TTL. Logical-0 may be a negative voltage in some CMOS circuits.

In *negative logic* these designations are reversed (i.e., high = logical-0 and low =logical-1). In the vast majority of uses positive logic is specified. In fact the descriptive names given to digital IC devices reflect a bias toward positive logic. This potential confusion is why I prefer high/low designations. For the illustrations and truth tables 1/0 is used, but recall that positive logic is implied.

#### **LOGIC FAMILIES**

A logic family is a series of IC devices that may be interconnected without interfacing; they use similar technology in their construction. All of the devices within a given family have the same input and output circuits; so direct interconnection is possible.

The only major consideration is whether an output can supply sufficient current to drive all of the inputs that are connected to it. In any given logic family output voltage and current levels, also input voltage and current requirements, are fixed by agreement and defined in terms of fan-in and fan-out.

The unit used to describe these terms in most cases is the current requirement of a single standard-input at the fixed voltage level. Such an

input has a fan-in of one unit. If a particular IC has a fan-out of five, this means that the device can drive five standard inputs. The device, therefore, can supply sufficient current to drive all five inputs satisfactorily. The total fan-in of all devices connected to any output must be equal to or less than the rated fan-out of the output.

The logic families considered are: RTL, DTL, TTL, HTL, ECL, and CMOS. Of these families CMOS and TTL are the most popular today RTL and DTL are obsolete and no longer used in new designs (although much of the older equipment, still in use, contains RTL and DTL devices).

#### SPEED VERSUS POWER

The principal factors governing the speed, or maximum operating frequency, of a digital IC are the internal resistances and capacitances. If resistances are increased, so that power consumption drops, then the resistance-capacitance time-constant of the device is increased. Long resistance-capacitance time-constants mean slower operating speeds. As a general rule, therefore, higher speed logic-families have high power requirements. CMOS devices, which require very little current (hence are low power), operate well only at 4 or 5 megahertz (MHz) with some devices operating as high as 10 MHz. TTL devices, on the other hand, usually work at 18 or 20 MHz, with some selected devices operating well over 80 MHz.

#### **RTL DEVICES**

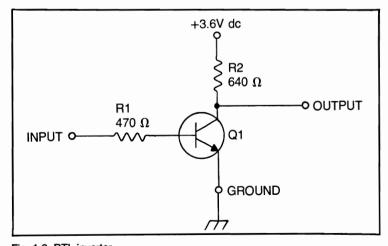

Resistor-transistor-logic (RTL) is an obsolete logic family that was popular in the early to mid-1960s. Figure 1-2 shows a typical RTL inverter circuit, i.e., a circuit that produces a low output when the input is high and a high output when the input is low.

RTL IC devices use 0 V for logical-0 (low) and +3.6 V for logical-1 (high). If the input of the RTL inverter is grounded (i.e., placed low), then the output voltage is high, which in this case means +3.6 V. If the input voltage is high, the output is 0 V.

Fig. 1-2. RTL inverter.

Fig. 1-3. DTL inverter.

RTL devices usually carry type numbers in the UL900 series (mostly 8 and 10 pin metal cans) and MC700 series (mostly 14 pin DIPS).

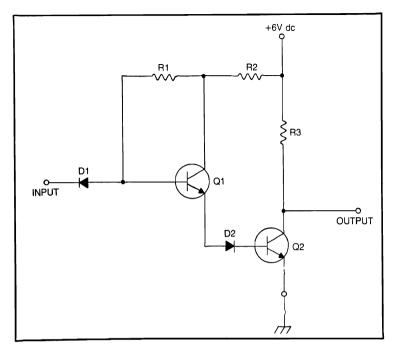

#### **DTL DEVICES**

The next popular IC logic family is diode-transistor-logic (DTL). These devices operate at speeds greater than most RTL devices. Figure 1-3 shows a typical DTL inverter.

When the DTL input is high, diode 1 is reverse-biased. In that condition resistor 1 forward-biases transistor 1, which in turn forward-biases diode 2 and transistor 2. Voltage levels in most digital circuits are selected to *saturate* the transistors; when transistor 2 (Q2) is turned on, it is turned on to full saturation. This means that the output of the inverter, which is the collector of Q2, goes within a few millivolts of ground.

When the input is low, the cathode of diode 1 (D1) is grounded. Since D1 is now forward-biased, the base of Q1 is essentially grounded. Under this condition Q1, D1 and Q2 are reverse-biased. With Q2 cut off, then, the output voltage rises to  $V_{CC}$  +.

Most DTL devices carry part numbers in the MC800 and MC900 ranges (Motorola designation).

#### TTL DEVICES

Probably the most widely used digital IC is the transistor-transistorlogic (TTL) logic family. When most people speak of digital ICs, it is the TTL family of devices to which they refer. Most TTL devices carry type numbers in the 5400 or 7400 series. Those devices that are in the 5400-series are military equivalents to the 7400-series device (i.e., a 5447 is a 7447 in uniform). The principal difference between the 5400 and 7400 devices is the operating temperature range (-55-+125 degrees C for mil-specified devices).

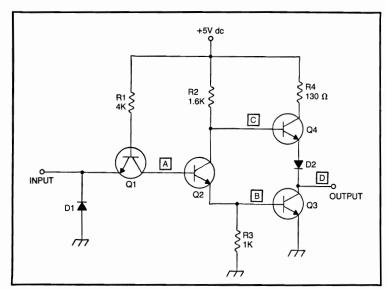

Figure 1-4 shows the circuit for a typical TTL inverter IC. Like the DTL device, the TTL input acts as a current source, while the output acts as a current sink. The typical TTL input sources 1.8 mA (milliamps) and is low if the voltage is 0-0.8 V, and high if 2.4-5.0 V are applied. Performance at values of input potentials between 0.8 and 2.4 V is not defined; so operation of the devices is unpredictable.

When the TTL input is high, Q1 is cut off; so point A goes high. This condition turns on Q2 forcing point B high and C low. You find, that Q3 is turned on and Q4 is off. This forces the output low. Again, the transistors are operated either totally cutoff or totally saturated (on).

If the input is low, then exactly the opposite situation occurs: Q1 is turned on (forcing point A low), Q3 is off, and Q4 is turned on; i.e., it is connected to  $V_{\text{CC}}$  +.

TTL devices must have a regulated dc power supply of +4.75-+5.2 V. In fact there are some circuits or combinations of devices that require a more limited range of voltages nearer to +5 V dc. Voltages greater than +5.2 V often result in a high failure-rate of TTL devices.

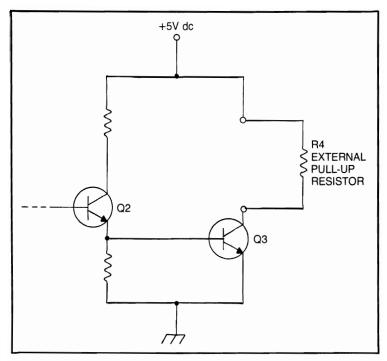

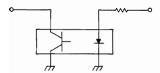

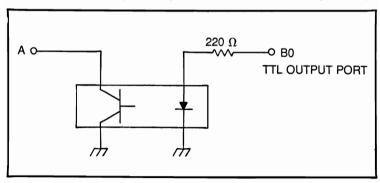

Some TTL devices are described as being *open-collector*. They are essentially the same as regular TTL devices, except that the output circuit is modified, i.e., Q4 and D2 are missing. An example of an open-collector circuit is shown in Fig. 1-5. These devices require an external 1000-2000 ohm resistor between the output terminal and the 5 V dc power supply line.

Fig. 1-4. TTL inverter.

Fig. 1-5. TTL open-collector circuit.

#### **CMOS DEVICES**

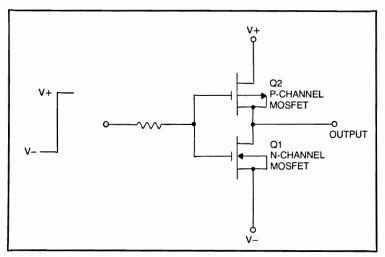

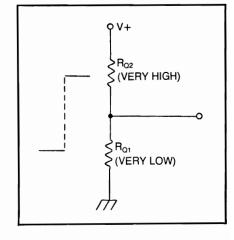

Complementary metal-oxide semiconductor (CMOS) IC's use field-effect transistors (MOSFET), instead of the PNP or NPN bipolar transistors that are used in other IC logic families. CMOS inputs, therefore, offer very high impedance. Figure 1-6 shows a typical CMOS inverter circuit. Note that this family is called complementary because the output circuit consists of a complementary pair of MOSFET transistors i.e., an n-channel and a p-channel in series.

CMOS devices can use a monopolar power supply, like TTL or DTL, or they can use a bipolar power supply similar to operational amplifiers. When bipolar supplies are used, the positive voltage can be any potential between +4 V and +15 V, while the negative voltage can be -4 V to -15 V. In monopolar cases the V+ can also be +4 to +15 V, while the V- is actually 0 V.

CMOS outputs are not directly TTL compatible, although some specific ICs in the CMOS line are designed to have a TTL output stage (i.e., the 4049 and 4050 devices). These TTL-compatible devices are often used to directly interface CMOS and TTL devices.

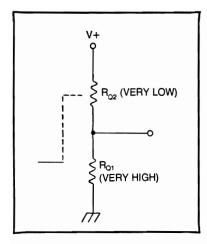

Figures 1-7 and 1-8 show the equivalent circuits for a CMOS inverter in both possible input conditions (i.e., input high and input low). A p-channel MOSFET turns on when the gate is low, while the n-channel device turns on when the gate is high.

Figure 1-7 shows the situation when the input is low. In this case Q1 has a very low (i.e., 200 ohm) channel resistance. The output is equivalent to a 200-ohm resistor to the positive-voltage power-supply line.

In Fig. 1-8 you see the situation when the input is high. Q2 now has a very high channel resistance, and Q1 has a very low channel resistance (again, about 200 ohm). In this case the output looks like a 200-ohm resistance to ground; so the output is low.

The high/low or low/high output transition in a CMOS device occurs at a point when the input voltage is midway between the positive and negative voltages. If the negative and positive voltages are not equal, the transition occurs at a potential of  $\frac{1}{2}((V+)-(V-))$ . If, on the other hand, negative and positive voltages are equal, the transition occurs at 0 V. If the negative-voltage potential is 0 V, the transition occurs at (V+)/2.

The CMOS output stage always looks like a high and low resistor in series across the power supply (reexamine Figs. 1-7 and 1-8); so negligible current is drawn from the power supply (it sees a low resistance load) when the input voltage is at the transition point. The overall current drain, therefore, is very small.

But CMOS devices do have a problem: they contain MOSFETs; so they are sensitive to static electricity. All A-series CMOS devices (e.g., 4001A) have this problem, but it is less severe in B-series (e.g., 4001B) devices. The B-series has built-in diode gate-protection to bypass high static potentials around the sensitive gate structure. Nonetheless, they should be handled with care.

#### **HTL DEVICES**

Noise pulses are often seen by logic circuits as valid input pulses. This problem is especially bothersome in high speed TTL devices that are normally able to pass high frequency, short duration, pulses. The solution in noisy environments is to use a digital-IC logic family that requires a high

Fig. 1-6. CMOS inverter.

Fig. 1-7. Circuit model for low input.

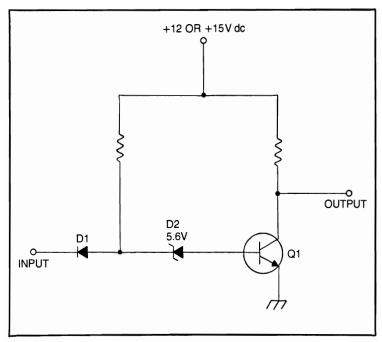

input-voltage to trigger. CMOS, operated at high negative and positive-voltage values, meets this requirement, but an older, bipolar, *high threshold logic* (HTL) can also be used (Fig. 1-9).

HTL (also called high noise immunity logic, or HNIL), uses positive voltages of 12 or 15 V, depending upon the series. As a result, the logic levels are also high; so it requires a bigger noise pulse to cause trouble.

#### EMITTER-COUPLED LOGIC

Up until now I have talked about saturated logic families, i.e., the transistors in the ICs are either all the way on or all the way off (cutoff or saturated). *Emitter-coupled logic* (ECL) is called an AC logic family because the transistors are operated in a nonsaturated mode. As a consequence, ECL devices are capable of very fast operation. Most commonplace ECL devices can operate at 80 or 120 MHz, while some costly, special purpose, devices can operate at over 1 GHz (thats 1000 MHz!).

The usual prescaler for a digital frequency counter is nothing more than an ECL frequency divider that divides the 500 MHz input signal down to 50 MHz.

It is necessary to use VHF/UHF circuit design and layout techniques when working with ECL devices. The frequencies are, after all, in the VHF and UHF ranges.

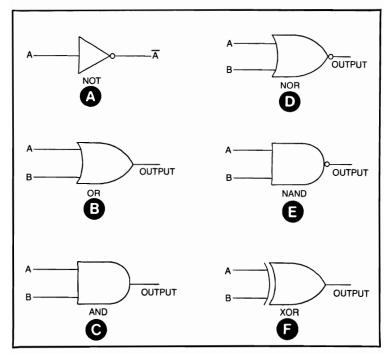

#### **GATES**

A digital electronic *gate* is a circuit that either passes a signal or refuses to pass a signal, according to well-defined rules. The basic types of digital electronic gates are NOT, OR, AND, NOR, NAND, and Exclusive-OR (also called XOR). In the following paragraphs I discuss all of these basic gates.

#### **NOT Gates (Inverters)**

NOT gates, also called inverters, produce an output that is the opposite of the input signal. Recall that digital circuits respond only to high and

low voltage levels. In an inverter circuit, therefore, the output is high when the input is low, and low when the input is high.

The circuit symbol for the inverter is shown in Fig. 1-10A Note that any digital symbol with a circle on the output produces an inverted output. Similarly, if one or more inputs have a circle, then they are inverted. The rules for the operation of the inverter are:

- •A high on the input produces a low output.

- •A low on the input produces a high output.

#### **OR Gates**

An OR gate passes a signal to the output if either input is high. The symbol for an OR gate is shown in Fig. 1-10B, while the truth table is given in Table 1-1B. The truth table shows the rules of operation for the gate. These are:

- •If both inputs A and B are low, the output is low.

- If either input A or B are high, the output is high.

- •If both inputs A and B are high, the output is high.

#### **AND Gates**

The AND gate is the opposite of the OR gate. The AND gate produces a high output only when both inputs are also high. The circuit symbol for the AND gate is given in Fig. 1-10C, and the truth table is shown in Table 1-1C. The rules for the operation of the AND gate are as follows:

- If both inputs A and B are low, then the output is low.

- •If either input A or B is low, then the output is low.

- •If both inputs A and B are high, then the output is high.

#### **NOR Gates**

The NOR gate is a combination of a NOT gate (inverter) and an OR gate, hence the designation NOR means "not OR." It is, therefore, an OR gate with an inverted output. The NOR gate is, in fact, sometimes represented in text books as an OR gate with an inverter following. The NOR

Fig. 1-8. Circuit for high input.

Fig. 1-9. HTL inverter.

gate symbol, shown in Fig. 1-10D, is an OR gate symbol with the circle denoting inversion at the output. The truth table for the NOR gate is shown in Table 1-1D and is also summarized below:

- •If both inputs A and B are low, then the output is high.

- •If either A or B input is high, then the output is low.

- If both A and B inputs are high, then the output is low.

#### **NAND Gates**

The NAND gate is a NOT-AND gate, i.e., an AND gate followed by an inverter. The symbol for the NAND gate is shown in Fig. 1-10E. This symbol is the AND gate symbol with the circle at the output to denote inversion.

The truth table for the NAND gate is shown in Table 1-1E. The rules are presented in summary below:

- •If both A and B inputs are low, the output is high.

- If either input A or B is low, the output is high.

- ●If both A and B are high, the output is low.

#### TTL AND CMOS EXAMPLES

Earlier in this chapter, I introduced several different families of digital-logic ICs. Several of these are considered obsolete and are not covered further. The TTL and CMOS families, however, are very much alive and form the basis of most digital design today.

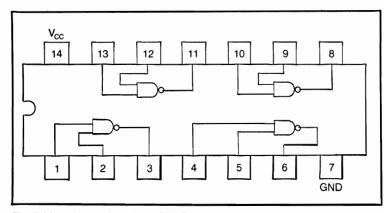

#### TTL/CMOS NAND Gates

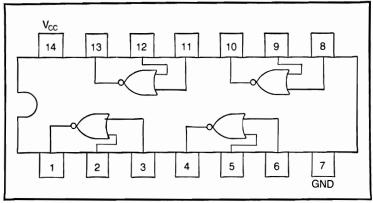

In the TTL IC family the most popular NAND gate is the 7400 (see Fig. 1-11). This device contains four two-input NAND gates, and usually sells for less than 25 cents, or around 6 cents per gate. Each of the four NAND gates in the 7400 package is an independent entity, but shares a common power supply and ground connection (pins 14 and 7, respectively).

The 7401 is similar to the 7400, however, the pin-outs are somewhat different, and it is an open-collector device. This means that pull-up resistors are needed, i.e., one 2-4-K ohm resistor from each output to the  $+5\,\mathrm{V}$  line.

The 7403 is also an open collector, but uses exactly the same pin-outs as the 7400. Of these three devices, the 7400 is by far the most popular.

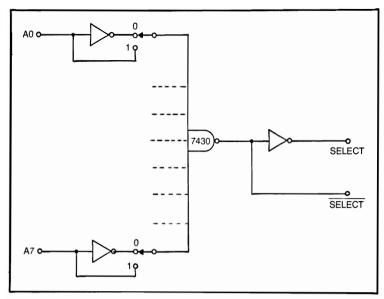

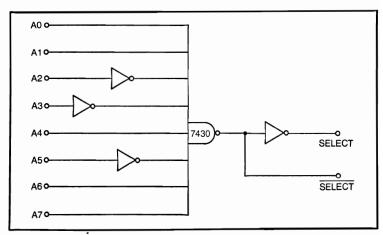

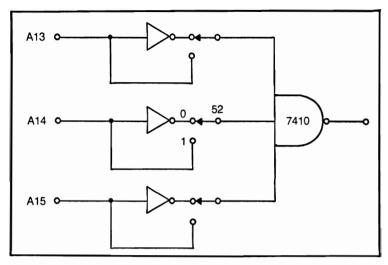

The 7430 is an eight-input NAND gate (one per 14-pin DIP package). The 7430 device, therefore, has eight distinct inputs. All eight must be high before the output drops low. If any one of the eight inputs remains low, then the output stays high. Since most microcomputers today are eight-bit machines, the 7430 is often used as an address or I/O-port decoder.

The 7410 and 7420 are three and four-input TTL NAND gates, respectively.

In the CMOS line there are several different types of NAND gates. The 4011 is a quad two-input NAND gate, reminiscent of the 7400. The current required for the CMOS device, however, is a lot lower than that required for the equivalent TTL.

Fig. 1-10. Digital logic symbols for gates.

OUTPUT OUTPUT 000-EXCLUSIVE OR (XOR) **⊕** § B œ INPUT INPUT ⋖ ⋖ Table 1-1. Truth Tables for the Gates of Fig. 1-10. OUTPUT OUTPUT MAN ON PA **©** g B œ INPUT INPUT ⋖ ⋖ OUTPUT -000 OUTPUT **⊙**§ **₫**¸ B INPUT INPUT -0 ⋖

12

The 4012 device is a dual four-input NAND gate. All four inputs of either gate must be high for its output to be low.

The 4023 device is a triple three-input NAND gate, while the 4068 is an eight-input NAND gate that is reminiscent of the TTL 7430 device.

#### TTL/CMOS NOR Gates

The 7402 TTL NOR gate is by far the most common example from the TTL line. It is almost as popular as the 7400. The pin-outs for the 7402 are shown in Fig. 1-12 (see Fig. 1-11 for comparison to the pin-outs to the 7400). Note that the pin-outs of the 7400 and 7402 are as different as their logic responses.

#### FLIP-FLOPS

All of the digital circuits I have discussed so far have operated in a transient manner. Once a pulse or any other input signal passes, the output state reverts back to its previous condition. Gates and inverters do not have any memory; so once the input passes, the resulting output also passes.

A flip-flop is a circuit that is capable of storing a single bit (i.e., a binary digit, either 1 or 0) of digital data. It remembers an input condition and holds the output after the data passes. There are various different types of flip-flop circuits, and they all operate on slightly different sets of rules. But, one thing that they all have in common is the ability to store a single data bit.

All common flip-flops can be made from various combinations of the basic AND, OR, NAND, NOT, NOR and XOR gates. The NAND, NOR, and NOT gates are used particularly often. Except for the two most simple flip-flops presented here, most electronic circuits use IC flip-flops instead of actual IC gates. It is simply too costly to make flip-flops from IC gates when the same manufacturers do all of the interconnection and offer the various flip-flops premade in IC form.

#### Reset-Set (RS) Flip-Flop

One of the simplest flip-flop circuits is the *reset-set*, or *RS*, flip-flop. Some textbooks call this type of circuit a *set-reset*, or *SR*, flip-flop.

Fig. 1-11. 7400 quad two-input NAND gate.

Fig. 1-12. 7402 quad two-input 7402 NOR gate.

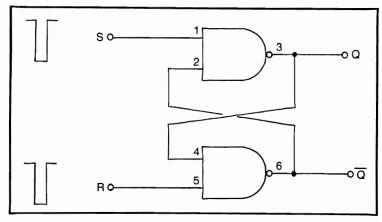

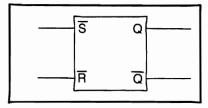

The RS flip-flop can be made from either two NAND gates or two NOR gates, although note that the operation of the two versions is slightly different.

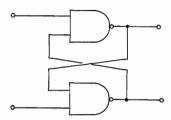

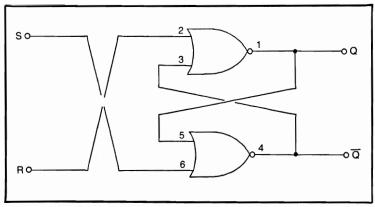

Figure 1-13 shows the circuit for RS flip-flop made from a pair of NAND gates (such as the TTL 7400 device, which contains four two-input NAND-gate sections).

There are two inputs required on the RS flip-flop; set (S) and reset (R). Also, there are usually two output terminals, which are complementary: Q and not-Q. *Complementary* means that one is low if the other is high. For example, when the Q output is high, then the not-Q is low. When the Q output is low, the not-Q is high.

The inputs of the NAND version of the RS flip-flop are active-low. Whenever you see an input that is designated as a not-input, or that has a bar over its symbol (i.e.,  $\overline{R}$ ), or that has a circle in the schematic diagram; it is an active-low input terminal. The circuit action of an active-low input occurs when the terminal is brought low. An example of the circled inputs as they are used in schematics is shown in Fig. 1-15, while the normal symbol for the RS flip-flop is shown in Fig. 1-14.

In most cases the absence of a bar over the letter, or of a circle at the input terminal in a drawing, indicates that the input is active-high. You sometimes see the exception when the RS flip-flop of Fig. 1-13 is shown as a square (similar to Fig. 1-14, but without the bars over the letters).

A momentary low on the set input of the NAND gate RS flip-flop causes the outputs to go to Q high and not-Q to low. Note that the term set usually means Q=high and not-Q=low. Reset indicates just the opposite: Q=low and not-Q=high. The flip-flop is said to have *memory* (and, indeed, solid-state computer memory devices use arrays of flip-flops); so the outputs stay in the set condition unless a reset pulse is applied to the R input.

The reset function is obtained by momentarily bringing the reset input low. This forces the Q output low and the not-Q output high.

The rules for operating the NAND-logic RS flip-flop are summarized in the truth table shown in Table 1-2. This truth table also lists two additional conditions. One of these is the condition in which both set and reset inputs

Fig. 1-13. NAND gate RS flip-flop.

are brought low simultaneously. This is a disallowed state, and the circuit does not know what to do; the output state is unpredictable. In the other condition both inputs are simultaneously high. In this condition you find that there is no change in the output state. The RS flip-flop simply remains in the condition present when the inputs were made high.

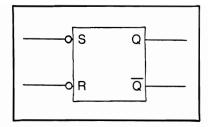

A NOR-logic version of the RS flip-flop is shown in Fig. 1-16. This circuit may be constructed from TTL 7402 NOR gates. Like the 7400 device, the 7402 contains four, independent, two-input gates (in this case, the NOR variety). The circuit in Fig. 1-16 performs differently from the NAND-logic version of Fig. 1-13. There are certain similarities, but a slightly different set of operating rules prevail.

The rules governing the NOR-logic RS flip-flop are summarized in the truth table of Table 1-3, but let's go over them briefly here:

- •If both inputs are low, there is no change in the output stage.

- If both inputs are simultaneously high, there is a disallowed state and the output condition is unpredictable.

- ●If the set input is made high momentarily, the output condition is Q=high and not-Q=low.

- If the reset input is made high momentarily, the output condition is Q=low and not-Q=high.

Note the principal difference between the two forms of RS flip-flop (examine the truth tables in Table 1-2 and 1-3 again). The NAND-logic RS flip-flop has active-low inputs, while the NOR-logic RS flip-flop has active-high inputs.

Fig. 1-14. Normal block diagram symbol.

Fig. 1-15. Block diagram symbol using circles, an alternate.

#### **Clocked RS Flip-Flops**

You can sometimes get into trouble with flip-flops that are too simple. You see, for example, electronic versions of the old fashioned relay race. In this classic problem with digital circuits, two relays may have slightly different actuation times. If the time difference causes them to operate out of sync, sometimes catastrophic results occur. Many of these problems are solved in digital electronics by using *clocked*, or synchronous, operation. In the case of the RS flip-flop, you get clocked operation by using the *master-slave* flip-flop, also called the *clocked RS flip-flop*.

The purpose of the *clock* (a train of pulses) is to synchronize the changes in the output condition by allowing them to occur only at certain times: during, or immediately following, a clock pulse. Most large-scale digital circuits use synchronous operation in order to keep things straight.

There are two basic forms of clocking used in RS flip-flops: level triggered and edge triggered.

A level-triggered flip-flop is one in which the output state changes in response to conditions on the inputs only when the clock input is either high or low (depending upon the type). Some level-triggered circuits require the clock pulse to be low for it to be active; the more common types require the clock pulse to be high.

An edge-triggered flip-flop allows state changes only during one of the two transitions of the clock pulse. The pulse must be in the process of going from low-to-high, or from high-to-low (again, depending upon type). A positive edge-triggered flip-flop, therefore, allows output changes to occur only on the positive-going transition (low-to-high) of the clock pulse. A

| s | R | Q            | Ισ |  |

|---|---|--------------|----|--|

| 0 | 0 | (DISALLOWED) |    |  |

| 0 | 1 | 1            | 0  |  |

| 1 | 0 | 0            | 1  |  |

| 1 | 1 | (NO CHANGE)  |    |  |

Table 1-2. Truth Table for Figs. 1-13-1-15.

Fig. 1-16. NOR-gate flip-flop.

negative edge-triggered flip-flop allows output transitions only on the negative-going (high-to-low) transition of the clock pulse.

It is important to remember the differences between these two types of triggering; so I'll reiterate them:

Level triggering means that changes can take place only during the time when the clock pulse is active, i.e., either high (positive level-triggered) or low (negative level-triggered).

Edge triggering means that output changes can take place only during the transition period of the clock pulse. A positive edge-triggered flip-flop changes only on the low-to-high transition, while a negative edge-triggered flip-flop wants to see the negative-going, or high-to-low, transition.

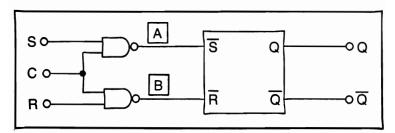

An example of a simple level-triggered, clocked, RS flip-flop is shown in Fig. 1-18. The main flip-flop is the same as the circuit in Fig. 1-13; it is shown here in block form for the sake of simplicity. The S and R inputs are controlled by a pair of NAND gates. When the clock pulse is low, both inputs of the RS flip-flop section (i.e., points A and B) see a high; so no changes can take place.

╗ S R Q 0 0 (NO CHANGE) 0 0 1 1 1 0 0 1 1 (DISALLOWED) 1

Table 1-3. Truth Table for NOR-Gate Flip-Flop.

Fig. 1-17. Symbol for NOR-gate flip-flops.

But, when the clock input goes high, the levels at points A and B (i.e., the S and R inputs of the flip-flop section) are controlled by the other inputs of the NAND gates. These inputs are used as the S and R inputs of the clocked flip-flop. If you wish to double-check this, review the operation of the NAND gates in this chapter.

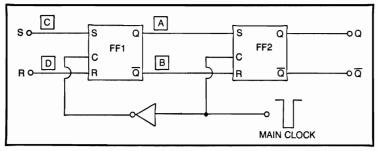

#### Master-Slave Flip-Flops

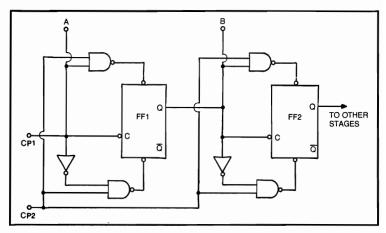

The use of clocking helps a great deal in taming the RS flip-flop. But several problems, again electronic versions of the old relay-race problem, can still pop up. Most of these are solved by using a slightly different approach, the so-called master-slave flip-flop. An example of the master-slave flip-flop is shown in Fig. 1-20. This circuit allows only one output state change per clock pulse (the clocked RS flip-flop allows continuous output-state changes as long as the clock input is active).

The master-slave flip-flop of Fig. 1-20 uses the clocked RS flip-flops of the previous example connected in cascade. The inverter shown in Fig. 1-20 allows you to drive the clock inputs of the two clocked-RS flip-flops out of phase with each other.

The clocked-RS flip-flop can change its output state only when the clock input is high, and then only in response to conditions on the R and S inputs. In the master-slave flip-flop, the main clock is kept high; so flip-flop 2 is active and flip-flop 1 is inactive.

When a clock pulse is applied, in this case a negative transition, flip-flop 1 becomes active, and flip-flop 2 becomes inactive. Note that the effect of the inverter is to make the clock input of flip-flop 1 high at this time. Any commands placed on the S and R inputs cause changes in the output of flip-flop 1 (i.e., points A and B in Fig. 1-20).

Because flip-flop 2 is inactive at this time (its clock input is low), changes at A and B are not yet reflected at its Q and not-Q outputs. Once the clock pulse has evaporated, the clock input of flip-flop 2 goes high again; so

Fig. 1-18. Circuit of the clocked-RS flip-flop.

Fig. 1-19. Symbol for the clocked-RS flip-flop.

the changes that took place on A and B can be transferred to action at the Q and not-Q outputs.

The synchronization occurs by keeping flip-flop 2 inactive when the low input stage is being set. Then flip-flop 1 is rendered inactive (forbidding further S and R input changes from affecting the output), while the data is transferred to flip-flop 2. This part of the sequence is called a load-transfer operation.

#### ADDITIONAL TYPES OF FLIP-FLOPS

So far I have considered two versions of the RS flip-flop (NAND-logic and NOR-logic) and two flip-flops that are derivative of the RS circuits, i.e., the clocked-RS flip-flop and the master-slave flip-flop. In the following sections I consider some more complex types of flip-flop: type-T, J-K, and type-D flip-flops. The latter circuit, the type-D, is also called a latch circuit.

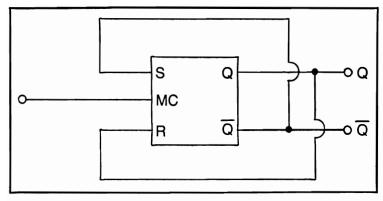

#### Type-T Flip-Flops

The type-T flip-flop (also called the *toggle flip-flop*) is shown in Fig. 1-21. This flip-flop circuit can be constructed by providing feedback connections (as shown) around an ordinary master-slave flip-flop. The master-slave flip-flop is constructed from a pair of RS flip-flops and an inverter stage. Note that the Q output is fed back to the reset input, and the not-Q output is fed back to the set input.

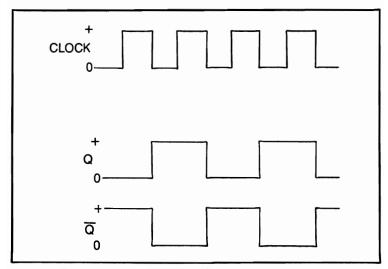

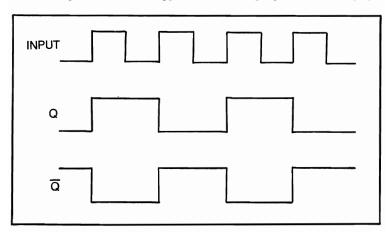

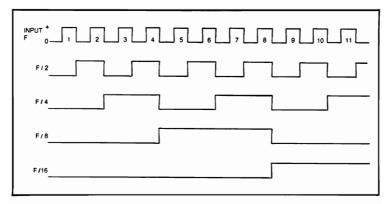

The type-T flip-flop functions as a binary divider, that is, the output signal has a frequency that is one-half (i.e., divided by two) of the input signal. The timing diagram for this circuit is shown in Fig. 1-22. Note that the Q output changes state only on negative-going transitions (i.e., high-to-low) of the clock pulse. At the first negative transition, the Q output snaps high and remains high until the clock input sees another negative transition. This condition occurs at pulse 2, at which time the Q output goes low again.

Fig. 1-20. Clocked flip-flop, type-T.

Fig. 1-21. Type-T flip-flop connection for binary division.

This is binary division of the input frequency; one output pulse is produced for each two input pulses.

There are sometimes differences found in terminal designations from one text or spec sheet to another. In Fig. 1-21, for example, I label the clock input MC for main clock. But, you are also likely to see T for toggle, or C for clock.

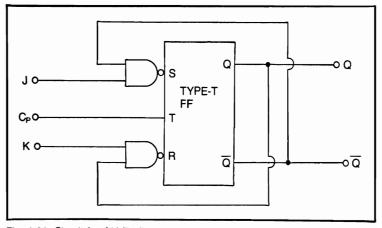

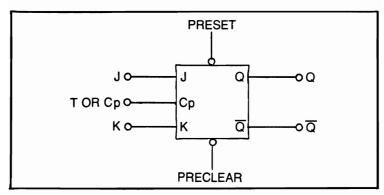

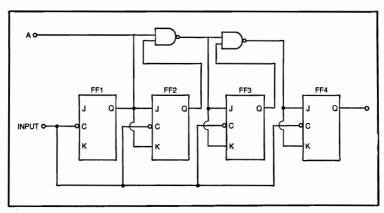

#### J-K Flip-Flop

One of the most useful, and perhaps most common, forms of clocked flip-flops is the J-K flip-flop. There are several advantages to the typical J-K flip-flop: (a) there are no invalid or disallowed states in the clocked mode, (b) it can cause the outputs to complement, and (c) in some IC versions it can provide nonclocked operation.

Fig. 1-22. Timing waveform of type-T flip-flop.

Fig. 1-23. Circuit for J-K flip-flop.

Figure 1-23 shows one of several popular ways to represent the J-K flip-flop. In this case, you see that it is a type-T flip-flop with the feedback to the set and reset inputs controlled by a pair of two-input AND gates. One input from each gate accepts the feedback lines, while the remaining inputs of the gates are used to form the J and K inputs of the flip-flop, respectively.

Figure 1-24 shows the circuit symbol for a J-K flip-flop. Not all versions of the J-K have the direct-mode input (*preset* and *clear*). However, preset and clear make it a more useful device. The preset input may also be called a direct-set input, and the preclear input called a direct-clear input.

**Direct Mode Operation.** The operation of the J-K flip-flops in the direct mode is very simple, and it is independent of conditions applied to the J and K inputs. The direct mode is controlled only by conditions on the preset and preclear input terminals. The rules are summarized in Table 1-5.

Direct mode input is active when low, so the only disallowed state occurs when both inputs are simultaneously low.

If the preset input is low, and the preclear input is high, then the outputs immediately go to a condition where Q is high and not-Q is low.

Fig. 1-24. Circuit symbol for J-K flip-flop.

Table 1-4. Timing Diagram for Clocked Operation of J-K.

| J | к | CLOCK | Q      | ā        |

|---|---|-------|--------|----------|

| 0 | 0 |       | (NO C  | HANGES)  |

| 0 | 1 |       | 0      | 1        |

| 1 | 0 | Y     | 1      | 0        |

| 1 | 1 |       | BINARY | DIVISION |

If the preclear input is made low, and preset input is high, then the outputs go to a state where Q is low and not-Q is high.

It is a general rule, when dealing with flip-flops of any type, that set or preset operations make the Q output high and the not-Q output low; while clear or reset operations work in just the opposite manner (i.e., Q low and not-Q high).

If both preset and preclear inputs are made high, then the flip-flop is ready for normal clocked-operation.

Clocked Operation. Whenever the preset and preclear inputs are simultaneously high, the J-K operates in the clocked mode. The rules for clocked operation are summarized in Table 1-4.

Like the type-T flip-flop, the J-K flip-flop (in the clocked mode) responds on the negative-going transition of the clock pulse. No output

Table 1-5. Timing Diagram for Nonclocked Operation of J-K.

| PRESET | CLEAR | CLOCK    | Q                     | a      |

|--------|-------|----------|-----------------------|--------|

| 0      | 0     | (DOESN'T | (DISALI               | _OWED) |

| 0      | 1     | CARE)    | 1                     | 0      |

| 1      | 0     |          | 0                     | 1      |

| 1      | 1     |          | ( CLOCKED OPERATION ) |        |

Fig. 1-25. Type-D flip-flop circuit.

changes occur, regardless of changes at the J and K inputs— until one of these negative-going clock-pulse transitions is seen. The outputs then respond according to the J-K input conditions. The rules for clocked operation are as follows:

- If both J and K are low, the flip-flop is inert and does nothing. No changes occur in the outputs.

- ●If J is low and K is high, the clocking makes Q low and not-Q high.

- ●If J is high and K is low, the clock-pulse transition makes Q high and not-Q low.

- ●If both J and K are high, the J-K flip-flop behaves much like a type-T flip-flop; clocking complements the outputs. This means that negative-going clock-pulse transitions force the outputs to go to the opposite state. The output waveform of the J-K flip-flop is then identical to the output waveform of the type-T flip-flop given in Fig. 1-22.

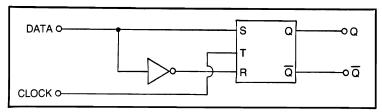

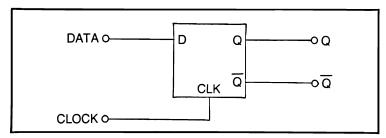

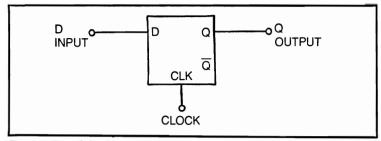

#### Type-D Flip-Flop

The type-D flip-flop circuit is shown in Fig. 1-25; an equivalent circuit is shown in Fig. 1-26.

The equivalent circuit consists of a clocked-RS flip-flop in which the set and reset inputs are fed by the same signal, but are 180 degrees out of phase with each other (i.e., complementary input). An inverter between the S and R lines accomplishes this neat trick.

The common line to the RS-inverter is called the data, or D, input instead of R and S. This input is usually labeled D on schematics.

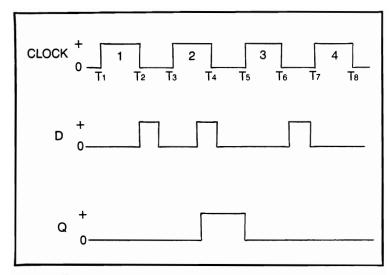

The rule for operation of the type-D flip-flop is very simple: data appearing on the input is transferred to the Q output only when the clock line is high.

•If the clock line is high, the output follows changes in the input signal (i.e., changes on the data input). When the data-input line goes high, the output

Fig. 1-26. An equivalent circuit for the type-D flip-flop.

Fig. 1-27. Typical timing diagram for type-D flip-flop.

goes high. Similarly, when the D-input line goes low, the output follows by also going low.

• If the clock line is low, then the output retains the last data that existed on the data-input line at the instant the clock line dropped low.

These rules can also be seen in the timing diagram of Fig. 1-27. Read the description below, keeping in mind the two rules given above:

- a. When the first clock pulse arrives (T1-T2), the data-input line is low; so the Q output goes low. (Internal timing in a microcomputer is kept by clock-pulse cycles; a complete clock-pulse cycle is a T-state, designated by T).

- b. During interval T2-T3, the data input goes high; but since no clock pulse is present, it cannot affect the output conditions.

- c. At the beginning of interval T3-T4, clock pulse 2 is high, but the data input is low. The output, therefore, must remain low.

- d. About midway through clock pulse 2, however, the data input goes high, forcing the Q output to also go high.

- e. The Q output stays high even after clock pulse 2 goes low.

- f. At the onset of clock pulse 3, the data input is low; so the Q output drops low also.

- g. The pulse on the data-input line during the interval T6-T7 cannot affect the  ${\bf Q}$  output because the clock is low.

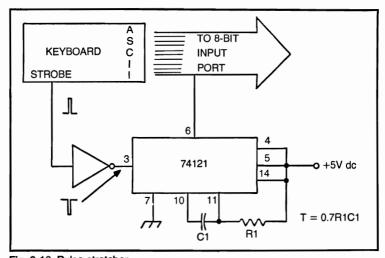

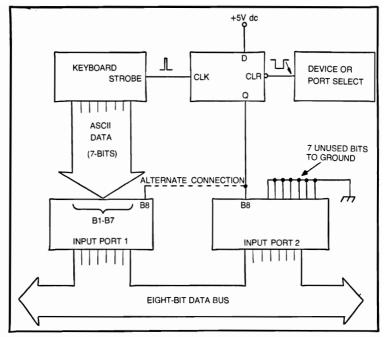

The so-called data latch is a special case of the type-D flip-flop. This device is used in digital readout circuits (i.e., in frequency counters) to hold current data until the new data is updated and ready for display. This gives the illusion that the data is updated instantaneously. In most cases the clock input is called a strobe input. Data at the input is transferred to the outputs only when the strobe line is high. The idea is to momentarily bring the strobe line high when the data at the input is valid, and then let the strobe line go low again until the next new data is ready.

#### MULTIVIBRATORS

So far, I have discussed the various digital-IC logic-families, assorted types of gates, and flip-flops. Now let's turn to the topic of *multivibrators*.

A multivibrator is basically a pulse-producing circuit. There are three basic forms of multivibrator: *monostable*, *bistable* and *astable*. It takes very little imagination to detect that these designations refer to the possible output states for each circuit.

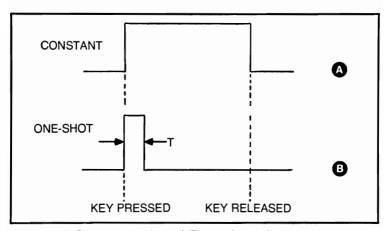

The monostable multivibrator has only one stable state (usually the state in which Q=low—but not always). Triggering the monostable multivibrator causes Q to go high for a time, but since this is not a stable state Q drops low again when a predetermined time period has elapsed.

Monostable multivibrators are also called one-shot circuits, and also (erroneously, albeit graphically) pulse stretcher circuits. The latter label is a misnomer because the circuit does not actually stretch a pulse, but generates a new pulse that has a longer period.

The bistable multivibrator has two stable states. It can remain in either state (i.e., Q=low or Q=high) indefinitely. The RS flip-flop is an example of a bistable multivibrator.

The astable multivibrator has no stable states. It is incapable of remaining in either Q low or Q high states. The Q output of the astable multivibrator flips back and forth between the high and low states, producing a square-wave pulse-train output. For this reason the astable circuit is usually used to produce the clock pulse found in digital circuits.

There are several ways to produce each of these types of multivibrator. Let's examine a few circuits built from discrete gates and the integrated circuits. Some IC devices, like the 555 timer, operate in either the monostable or astable modes. Here, I won't consider the circuits in which discrete transistors and resistors form the multivibrator.

When people speak of bistable multivibrators they are actually talking about the RS flip-flop. The RS flip-flop can remain in either Q=low or Q=high states. These conditions only change when an input signal commands the circuit to change. It can remain in either state indefinitely.

The monostable multivibrator, or one-shot, has only one stable state. In most circuits the stable state is Q=low. When the input of the monostable is triggered, the output snaps high for a certain period of time and then drops low again. The monostable multivibrator, then, produces one output pulse for each pulse received at the trigger input. This is why the monostable multivibrator is sometimes called the one-shot.

There are a number of reasons why you might want a one-out-for-one-in circuit. One of the most common is to stretch pulses. A very rapid input pulse, even in the nanosecond range, can be used to trigger monostable circuits that produce output-pulse periods from nanoseconds to days. The duration of the output pulse is usually much longer than the duration of the input trigger-pulse. In so-called pulse-stretcher circuit-applications, the output of the one-shot is used to substitute for the shorter trigger-pulse.

Most monostable multivibrators do not respond to further input trigger-pulses until the period of the output pulse has "timed out," i.e., the output has returned to its stable state. Monostables that do not respond to further trigger-commands until the output duration has expired are called nonretriggerable monostables.

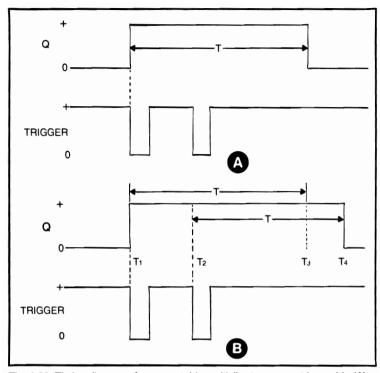

Fig. 1-28. Timing diagrams for monostable multivibrators, nonretriggerable (A), and retriggerable (B).

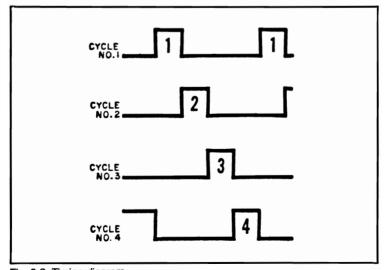

Some one-shot circuits are *retriggerable*, meaning that they respond to further input trigger-commands while the one-shot is in the unstable state, i.e., before it has timed out. Consider Fig. 1-28 to see how this might work. Figure 1-28A shows the operation of the regular nonretriggerable one-shot multivibrator. The first trigger-pulse causes the output to go high, and it remains high for period T. A second trigger-pulse has no affect of the one-shot because it occurs before T expires.

Now consider Fig. 1-28B. This is a timing diagram for the retriggerable monostable multivibrator. The output goes high when the first pulse arrives. But, before T expires a second trigger pulse is received. This second pulse causes the one-shot to retrigger; so the output remains high for an additional period T. Note that the total duration of the high state is not 2T, but T plus the portion of the first period that expired prior to the second trigger (i.e.,  $T + (T_2 - T_1)$ .

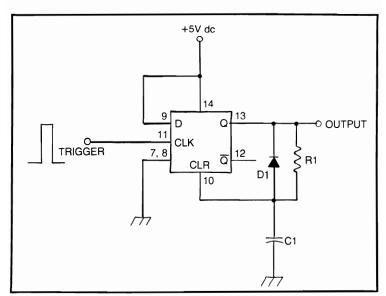

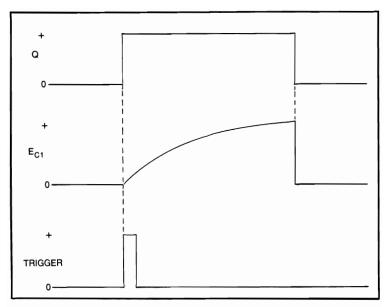

An example of a monostable multivibrator built from a CMOS type-D flip-flop is shown in Fig. 1-29. Recall the rules for the type-D flip-flop: (1) when D is high, a high is transferred to the Q output when the clock line goes high, and (2) when the clear line goes high the Q output is forced low.

The operation of the one-shot circuit in Fig. 1-29, is as follows: 1. When the circuit is at rest, Q is low and any charge on capacitor 1 is drained off through diode 1. 2. When a trigger pulse is received by the clock input, Q goes high. When Q is high, capacitor 1 charges through resistor 1.

3. When capacitor 1 has charged to a potential of approximately 2 V, the CLEAR input thinks it is high; so the flip-flop forces Q low.

4. The period that Q was high, i.e., the period of the one-shot, is determined by the time constant of resistance-capacitance 1, the potentials of the Q output, and the point at which the CLEAR input thinks that it is high instead of low.

The circuit in Fig. 1-29A uses a diode (D1) across the timing resistor (R1) to discharge the capacitor (C1) during the period when Q is low. This diode i not strictly necessary, but serves to speed up the circuit considerably. Without D1 the charge on the capacitor bleeds through the resistor. This requires another resistance-capacitance1 time-constant before the voltage across C1 discharges enough to permit retriggering of the one-shot. The purpose of D1 is to rapidly discharge C1 so that retriggering can occur almost immediately after Q drops low (see the waveform in Fig. 1-30B).

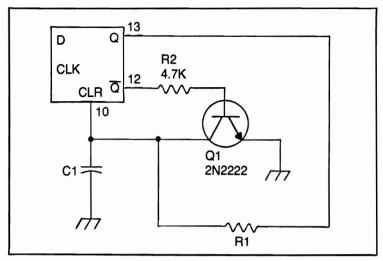

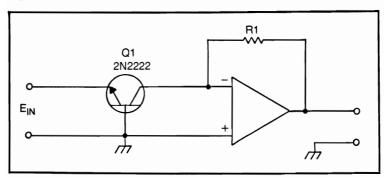

But the use of D1 creates a little problem. The charge potential across C1 cannot drop lower than the function potential of the diode (200 to 300 millivolts in germanium types and 600 to 700 millivolts for silicon types). Figure 1-31 shows the circuit for a modified version that uses a switching transistor (Q1) to discharge C1. The base of transistor Q1 is driven by the not-Q output.

#### SHIFT REGISTERS

A flip-flop is able to strobe a single bit of digital data. When two or more flip-flops are organized to store multiple bits of data, they constitute a *register*. Most registers are merely specially-connected arrays of flip-flops.

Fig. 1-29. CMOS 4013 type-D flip-flop as a monostable multivibrator circuit.

Fig. 1-30. Timing waveforms of monostable multivibrator.

There are several different circuit configurations that are called registers. They are classified by the method of which data input and output to and from the register. For example, *serial-in/serial-out* (SISO), *serial-in/parallel-out* (SIPO), *parallel-in/parallel-out* (PIPO), and *parallel-in/serial-out* (PISO).

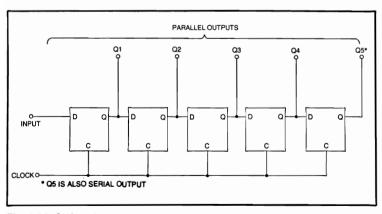

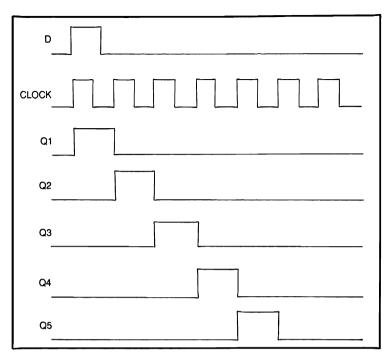

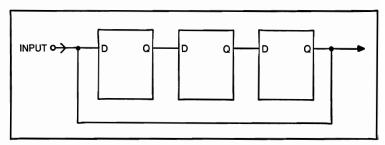

Figure 1-32 represents both SISO and SIPO shift-registers. The only significant difference is the parallel output lines on the SIPO register are absent on the SISO register.

The SIPO shift-register consists of a cascade chain of type-D flip-flops that have their clock lines connected. Recall the rules for type-D flip-flops: data can be transferred from the input to the Q output only when the clock input is high. The input can change at will; the output remains the same—as long as the clock line is low. But, if the clock line goes high, then Q output follows the data input. The Q output retains the last valid data that is present before the clock drops low again.

This rule can be applied to the situation shown in Fig. 1-33 which shows the transmission of a single bit of data from left to right through a SISO shift-register.

At the occurrance of the first clock-pulse, the input line is high. This point is the data-input line flip-flop 1; so a high, which is applied to the data input of the second flip-flop, remains after the clock pulse disappears.

When the second clock-pulse arrives, flip-flop 2 sees a high on its data input, and flip-flop 1 sees a low on its data input. This situation causes a low at Q1 and a high at Q2.

The third clock pulse sees a low condition of the data inputs of flip-flop 1 and flip-flop 2, and a high at the input of flip-flop 3. The third clock-pulse, then, causes Q1 and Q2 to be low and Q3 to be high.

Fig. 1-31. Modifying the circuit for retriggerable operation.

Note that the SISO input remains low after the initial high during clock-pulse 1. This means that the single high condition is propagated through the entire SISO shift register—one stage at a time. The high bit shifts position one flip-flop to the right each time a clock pulse arrives.

If the data at the input changes, the bit pattern at that input is propagated through the shift register.

The shift register in Fig. 1-32 is a five-bit, or five-stage, register (any bit-length can be selected). On the sixth clock-pulse, therefore, the high is propagated out of the register; so all flip-flops are now low.

The SISO shift register can be made into a SIPO device by adding parallel output lines at Q1, Q2, Q3, Q4, and Q5.

One use for the SIPO register is serial-to-parallel binary-code conversion. For economic reasons digital data is usually transmitted as a serial

Fig. 1-32. Shift register.

Fig. 1-33. Timing diagram for shift register.

stream of bits, i.e., the bits of the digital word are sent over a communications link. But, most computers and other digital instruments use a parallel form of data entry. Parallel data transfer is more expensive, but is considerably faster than serial transmission. If, for example, you have an eight-bit system, you need an eight-stage SIPO shift-register to convert the serial code to parallel form. The code is entered into the SIPO register one bit at a time. After eight clock-pulses the first bit appears at Q8 and the last bit at Q1.

Parallel-entry shift-registers are faster to load than serial-input shift-registers. This is because a single bit can be changed, if necessary. To change a single bit of data in the serial type requires you to ripple through the entire contents.

There are two basic forms of parallel data-entry: parallel and jam.

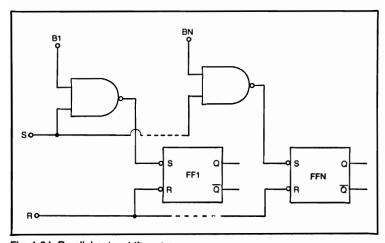

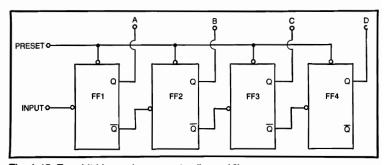

In parallel entry, shown in the partial schematic of Fig. 1-34, the register must first be cleared (i.e., all bits set to zero) by bringing the reset line momentarily low. The data that is applied to inputs bits 1-n can be loaded into the register by momentarily bringing the set line high.

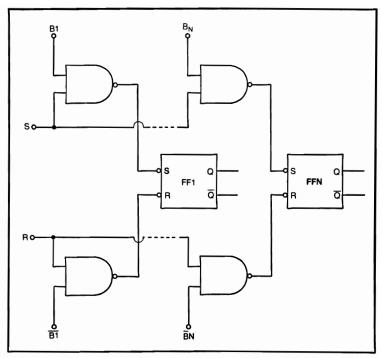

The jam-entry circuit of Fig. 1-35 is able to load data from bits 1-n onto the other inputs. While this may not look superior at first glance, it is because IC shift-registers using this technique have internal inverter stages at the complementary inputs. These inverters have their inputs connected to the noncomplemented inputs; so the outside user never sees the complementing process.

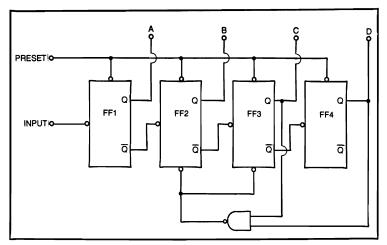

A recirculating shift-register is shown in Fig. 1-36. Since the output of a serial shift-register allows the outside world to see only one bit at a time, you must empty the entire contents of the shift register in order to read these contents. Ordinarily that would destroy the data, because the input would be either high or low during the entire operation. A single read operation would fill the register with all ones or zeros. The recirculating shift register connects the output (serial output) back to the input; so a read operation automatically rewrites the data back into the shift register.

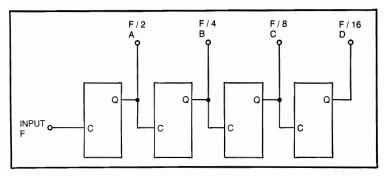

# **DIGITAL COUNTERS**

A digital counter is a device or circuit that operates as a frequency divider. The most basic form of digital counter is the J-K flip-flop connected with the J and K inputs tied high (i.e., placed in the clocked mode). This produces one output pulse for every two input pulses. It is a binary, or divide-by-two, counter.

These fancy digital-frequency period-counters are nothing more than digital divide-by-ten counters connected so that the binary-coded output is converted to a decimal display.

There are two basic classes of digital counter circuits: serial and parallel. The serial counters are called *ripple counters* because a change in the input must ripple through all stages of the counter to its proper point. Parallel counters are also called synchronous counters.

In a ripple counter the data is transferred serially, which means that the output of one stage becomes the input of the next stage.

The basic element in most counters is the J-K flip-flop (Fig. 1-37). Note in the figure that the J and K inputs are permanently tied high; they remain active.

A timing diagram for this divide-by-two circuit is shown in Fig. 1-38. It shows the action of the circuit. Outputs of the J-K flip-flop change state on negative-going transitions of the clock pulse. In Fig. 1-38 the first negative-going transition causes the Q output to go high. Q remains high

Fig. 1-34. Parallel entry shift register.

Fig. 1-35. Jam entry.

until the input sees another negative-going clock-pulse. At that time the output drops low. The action required to make a complete output requires two clock-pulses; so this J-K flip-flop is dividing the input frequency by two.

You can make a binary ripple-counter by cascading two or more stages, as shown in Fig. 1-39. This particular circuit uses four J-K flip-flops in cascade. Any number, however, can be used.

The major problem with this type of counter is that only those division ratios that are powers of two can be accommodated. In the four-stage circuit shown the possible division ratios are 2, 4, 8, and 16.

Frequency division is one major use for a counter circuit. In some electronic instruments, for example, you may want to prescale a frequency.

Fig. 1-36. Recirculating shift register.

Fig. 1-37. J-K flip-flop as a binary divider.

i.e., divide it by some other frequency to a lower frequency that can be handled by a digital counter or other digital instrument.

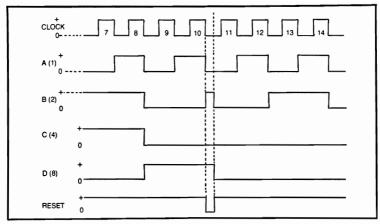

This is only one application for the counter circuit. One of the most common applications is to count; i.e., the total number of pulses that pass. Consider again the circuit of Fig. 1-39 and the timing diagram of Fig. 1-40. Outputs A, B, C, and D are coded in binary, A being the least significant bit and the D the most significant. These are weighted in a 1-2-4-8 code system to represent decimal or hexadecimal digits. These figures are the normal weights of the binary number system.

Consider the timing diagram of Fig. 1-40. Note that all B output changes occur following the arrival of a pulse. After pulse 1 has passed, the QA line is high and all others are low. This means that the binary word on the output lines is  $0001_2$  (i.e.,  $1_{10}$ ); one pulse has passed.

Following pulse 2 you expect  $0010_2$  (i.e.,  $2_{10}$ ); because two pulses have passed. Note that QB is high and all others are low. The digital expression is  $0010_2$ .

The counter in Fig. 1-39 is called a modulo-16 counter, a base-16 counter, or a hexadecimal counter.

The output of a hexadecimal counter can be decoded to drive a display device that indicates 0-9 (i.e., decimal) or 0-F (hexadecimal). A decimal readout is provided in most applications where people read the display.

Fig. 1-38. Timing diagram for J-K flip-flop.

Fig. 1-39. Frequency divider (four stage) circuit.

## **Decimal Counters**

A decimal counter operates in the base-10, or decimal, number system. The most significant bit of a decimal counter produces one output pulse for every ten input pulses. Decimal counters are also sometimes called decade counters. The decimal counter forms the basis for digital-event, period, and frequency-counter instruments. Thus, the hexadecimal counter in Fig. 1-39 is not suitable for decimal counting unless it is modified for base-10 operation.

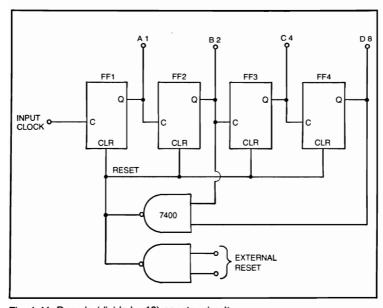

Figure 1-41 shows a TTL hex-counter modified by adding a single TTL NAND-gate. Recall that a TTL J-K flip-flop uses inverted inputs for the clear and set functions. As long as the clear input remains high, the flip-flop functions normally. When the clear input is momentarily brought low, the Q output of the flip-flop goes low.

The decade counter in Fig. 1-41 is connected so that all four clear-inputs are tied together to form a common clear-line. This line is connected to the output of a TTL NAND-gate (i.e., one section of a 7400 device). Recall the rules of operation for the TTL NAND-gate: if either input goes low, the output goes high. But, if both inputs are high, the output goes low.

The idea behind the circuit of Fig. 1-41 is to clear the counter to 0000 following the tenth input pulse. Let's examine the timing diagram in Fig. 1-42 to see if the circuit does the correct thing. Up until the tenth pulse, this diagram is the same as the diagram for the base-16 counter.

The output of the NAND gate keeps the clear line high for all counts through ten. The inputs of this gate are connected to the B and D. The D line stays low, forcing clear high, until the eighth input pulse passes. At that time (i.e., T0 in Fig. 1-41), D goes high and bit B drops low; so the clear line remains high for the ninth pulse.

The clear line remains high until the end of the tenth pulse. At that point T2) both B and D are high; so the NAND-gate output drops low, clearing all four flip-flops (i.e., forcing them to the state where all four Q outputs are low). The counter is, therefore, reset to 0000.

The reset counter produces a 0000 code; so the B and D outputs are now low, forcing the clear line high again. The entire reset cycle occurs during period (T3-T2). This period has been expanded greatly for illustration in the figure, but actually takes only nanoseconds or microseconds.

Fig. 1-40. Timing waveform.

The eleventh pulse increments the counter one time, so the output is 0001<sub>2</sub>. The count sequence in decimal is 0-1-2-3-4-5-6-7-8-9-0-1, etc. The output code is a ten-digit version of four-bit binary (hexadecimal), called binary coded decimal (BCD).

# **Synchronous Counters**

Ripple counters suffer from one major problem—speed. The counter elements are wired in cascade; so an input pulse must ripple through the entire chain before it affects the output. A synchronous counter feeds the

Fig. 1-41. Decade (divide-by-10) counter circuit.

Fig. 1-42. Waveform of decade counter.

clock input to all flip-flops in parallel, and this results in a much faster operation.

Figure 1-43 shows a partial schematic for a synchronous binary counter. You can accomplish synchronous operation by using four flip-flops with clock inputs tied together and a pair of AND gates.

One AND gate is connected so that both Q1 and Q2 are high before flip-flop 3 is active. Similarly, Q2 and Q3 must be high before flip-flop 4 is made active. On a clock pulse any of the four flip-flops scheduled to change do so simultaneously. Synchronous counters attain faster speeds, although ripple counters seem to predominate most applications.

## **Preset Counters**

A preset counter increments from a preset point instead of 0000. For example, suppose you want to count from  $5_{10}$  (0101<sub>2</sub>). Preset the counter to 0101 and increment from there.

Fig. 1-43. Synchronous binary counter.

Fig. 1-44. Presettable counter.

Figure 1-44 shows a common method for achieving preset conditions, the jam input. Only two stages are shown here, but adding two more stages makes it a four-bit counter. Of course, any number of stages can be connected in cascade to form an n-bit preset-counter.

In Fig. 1-44, the preset count is applied to points A and B, and both bits are entered simultaneously when the line for clock pulse 2 is brought high. This line is sometimes called the enter or jam terminal.

Once the preset bit-pattern is entered, the counter increments with every transition of the clock line 1.

#### **Down Counters**

A down counter decrements, instead of incrementing, the count for each excursion of the input pulse. If the reset condition is 0000, then the next count is 0000–1, or 1111.

For the down counter use basically the same circuit as before, but toggle each flip-flop from the not-Q, rather than the Q, of the preceding flip-flop. An example of a four-bit binary down-counter is shown in Fig. 1-45. Note that the outputs are taken from the Q outputs of the flip-flops, but that toggling is from not-Q.

Fig. 1-45. Four-bit binary down counter (base-16).

Fig. 1-46. Base-10 down counter.

The preset inputs of the flip-flops are connected to provide a means to preset the counter to its initial (i.e., 1111) state. This counter is also called a subtraction counter because each input-pulse causes the output to decrement by one bit.

A decade version of this circuit is shown in Fig. 1-46. As in the case of the regular decade counter, a NAND gate is added to the circuit to reset the counter following the tenth count. Detect the states where outputs C and D

Fig. 1-47. Up/Down Counter.

are high, and then clear the two middle flip-flops. This action forces the output to  $1001_2$  (i.e.,  $9_{10}$ ). The counter then decrements from 1001 in the decimal sequence 9-8-7-6-5-4-3-2-1-0-9, etc.

# **Up/Down Counters**

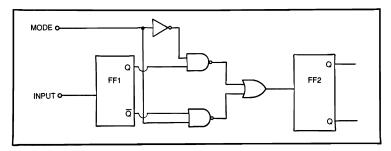

Some counters operate in both up and down modes, depending upon both the logic level applied to a mode input. Figure 1-47 shows a representative circuit, in which the first two stages of a cascade counter are modified by the addition of several gates. If the mode input is high; the circuit is an up counter. If the mode input is low; the circuit operates as a down counter.

# Chapter 2

# **Interfacing Digital IC Families**

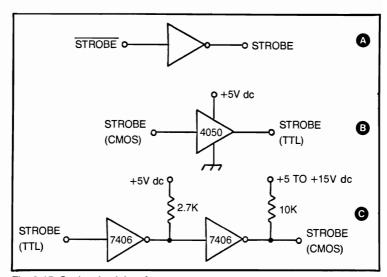

Although there have been several IC logic families available over the years, only two main families have been popular in microcomputer electronics: TTL and CMOS (and CMOS derivatives such as NMOS). The typical microcomputer might be a CMOS or NMOS device; all but a few have TTL-compatible output-lines and operate from the +5 V power-supply typical of TTL devices. In this chapter I discuss some techniques for interfacing different IC digital-logic families to each other.

The TTL logic family uses 0 V for low and  $\pm$ 5 V for high. The CMOS family, on the other hand, might use the TTL levels but also can use anything between  $\pm$ 4.5 and  $\pm$ 18 volts for the high to low levels. Clearly, some means of interfacing is needed.

There are several families of TTL logic, and they are differentiated in their respective parts numbers. The L and LS devices (e.g., 74LS00 or 74L00) are lower-current versions of the regular TTL devices. Any CMOS output drives one L or LS TTL-gate. As long as the CMOS device is operated from only a  $\pm 5$  V dc power-supply, you can get away with simply connecting the CMOS output to the L or LS TTL-input. The 4001A and 4002A (not the B versions!) also drive one regular TTL-input.

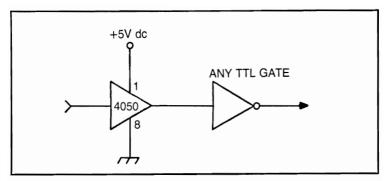

There are three CMOS devices that drive up to two (regular, L or LS TTL-gates. These are the 4049, 4050, and 4502 devices. The 4049 device is a hex inverter, while the 4050 is a noninverting hex buffer. The 4502 device is a Tri-state hex inverter, which means that the output lines float at a high impedance unless a *chip-enable* line is active. These devices are capable of directly interfacing CMOS outputs to TTL inputs. Figure 2-1 shows the typical circuit. Note that this only works if the 4049, 4050, or 4502 are operated from the +5 V power supply of the TTL circuits. The CMOS device that drives the 4049, 4050, and 4502 need not be a +5 V circuit; but should not be bipolar (e.g., it could be 0 to +12 V). If the 4050 is operated at any potential other than +5 V (applied to pin 1), the whole deal is off—the device won't interface with the TTL input to follow.

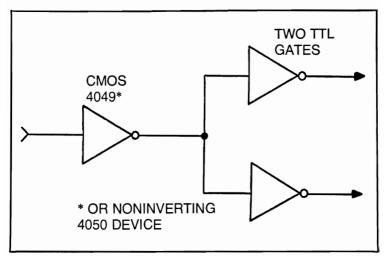

Figure 2-2 shows the connection of the 4049 (or 4050) device to interface up to two TTL-gates. If any larger number of TTL gates is

Fig. 2-1. Interfacing CMOS to TTL.

anticipated, as might be the case on a microcomputer bus, substitute a high-power bus-drive IC.

The 4050 device does not invert the input pulse. The 4049 and 4502 devices, however, are inverters and deliver a pulse to the TTL gate that is of opposite polarity from the main input pulse.

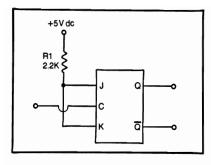

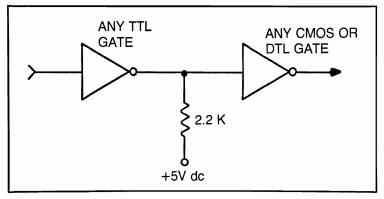

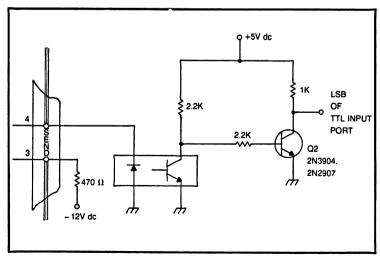

Figure 2-3 shows the connection required to interface a TTL output to a CMOS input. Remember that the TTL output line is a current sink (TTL inputs are current sources), while the CMOS input is the high-impedance gate of a MOSFET transistor. This means that you must provide a current source for the TTL output in order to interface with a CMOS input! In Fig. 2-3, a 2.2K ohm pull-up resistor to the +5 V line is used as the current source to keep the TTL output happy.

The CMOS device changes state only when the input voltage goes past the point that is equal to one-half the difference between the negative voltage and positive voltage power-supply limits. If a CMOS device is operated from 0 and a positive-voltage potential greater than +5 V, it is

Fig. 2-2. CMOS-to-TTL.

Fig. 2-3. TTL output to CMOS input.

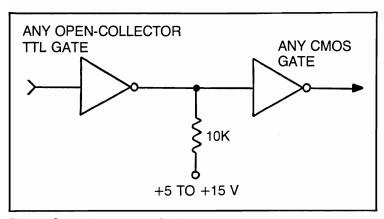

possible that the TTL device (which delivers only +5 V) will never reach transition-voltage of the CMOS device. For example, if the CMOS device is operated from +12 V, the trip point is +6 V; so no TTL device drives the CMOS properly—unless it is an open-collector TTL with an output that is also operated from +12 V. Figure 2-4 shows a circuit that accomplishes this neat trick.

Fig. 2-4. Open-collector TTL to CMOS.

The open-collector TTL device is operated from +5 V (as any TTL device, is), but there is no collector load (internally) on the output transistor. You must provide a pull-up resistor from the output to the positive-voltage line. The typical TTL open-collector output operates at least to +15 V, while some operate to +30 V. To interface with a CMOS device that is operated from more than +8 V dc, use an open-collector TTL-gate with a 10K ohm pull-up resistor to the CMOS power supply (not the TTL supply!).

# Chapter 3

# **Control Signals**

The control signals from a microprocessor chip either tell the outside world what the processor is doing or tell the processor something of what the outside world demands. Several such control signals are found on all microprocessors, and the status of these signals is of critical importance to the interface designer.

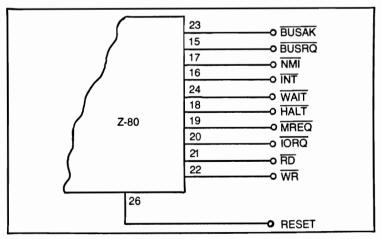

## **Z-80 CONTROL SIGNALS**

The Z-80 microprocessor was designed to be at least somewhat compatible with the 8080A device. The software instructions of the Z-80 are inclusive of the 8080A instructions, so there is definitely software compatibility (except for timing loops in some cases). The Z-80 device, however, uses a different set of control signals, as defined below. (For the pin-outs see Fig. 3-1.)

| RD                     | Indicates that the CPU (central processing unit) is reading something into the accumulator. This active-low output is |

|------------------------|-----------------------------------------------------------------------------------------------------------------------|

|                        | used for both input operations and memory read opera-                                                                 |

|                        | tions. Read.                                                                                                          |

| $\overline{\text{WR}}$ | This active-low output is the complement of the $\overline{RD}$ output                                                |

and is used to indicate that the CPU is writing data to either a memory location or an output port. Write.

This active-low output indicates that an input or output operation is taking place. This signal is used in conjunction with the WR and RD signals, as required by the type of operation. Input/output request.

This active-low output tells the outside world that a memory read or memory write is taking place. It is used in conjunction with the WR and RD signals, as needed. *Memory request*.

This active-low output indicates that a halt instruction has been executed. A halt can only be terminated by receipt of an interrupt.

IORQ

**MREQ**

| WAIT  | This active-low input causes the CPU to insert a specific number of clock periods before going on to the next in- |

|-------|-------------------------------------------------------------------------------------------------------------------|

|       | struction. This input is used by external peripherals or                                                          |

|       | memory that is too slow to keep pace with the CPU. The                                                            |

|       | external device drags the WAIT low in order to gain the                                                           |

|       | needed breathing time.                                                                                            |

| INT   | This interrupt line is sampled by the CPU at the end of the                                                       |

|       | execution of the current instruction. If INT is low, the CPU                                                      |

|       | executes the interrupt program. This interrupt line can be                                                        |

|       | masked by the condition of the CPU's interrupt flip-flop.                                                         |

|       | Interrupt request                                                                                                 |

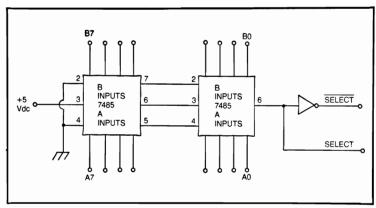

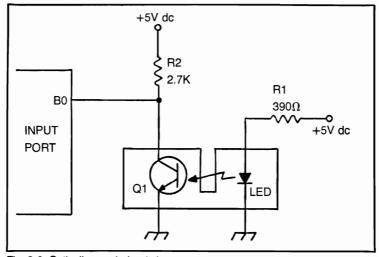

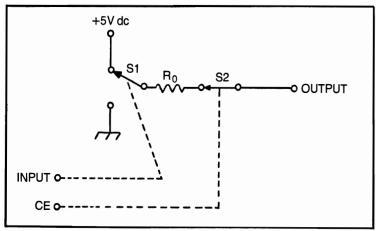

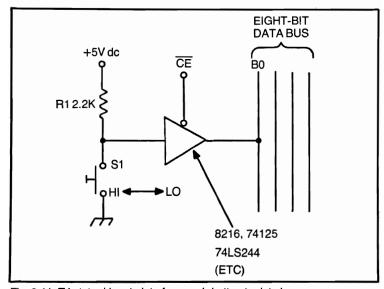

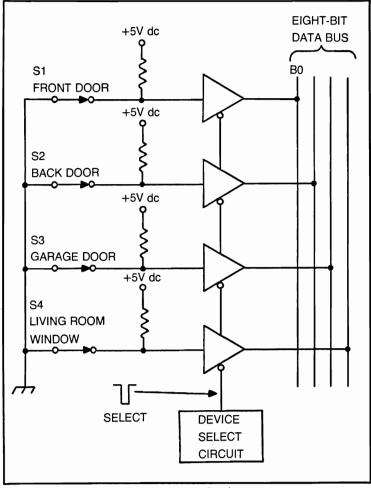

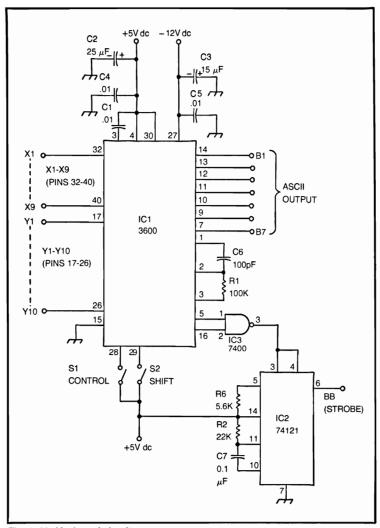

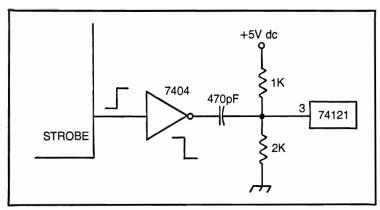

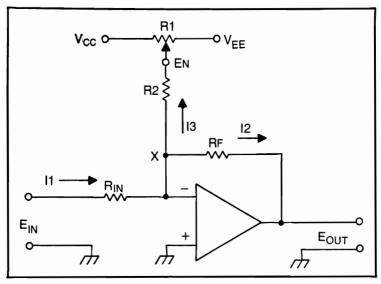

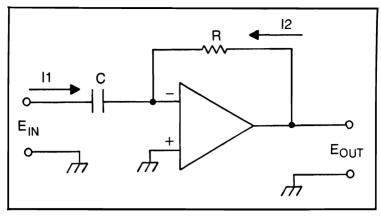

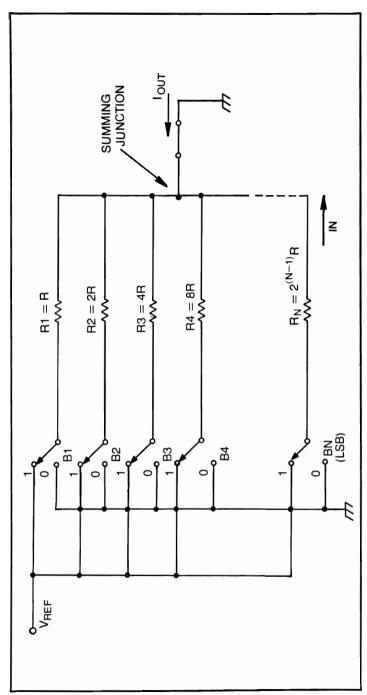

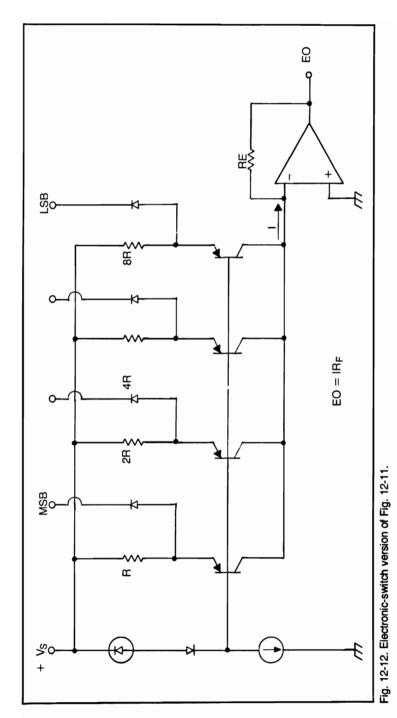

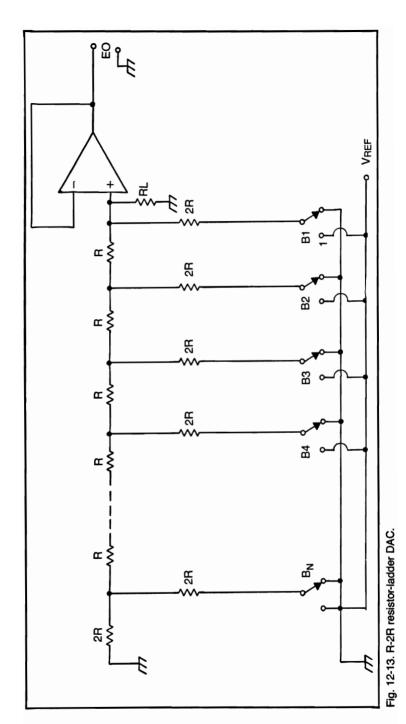

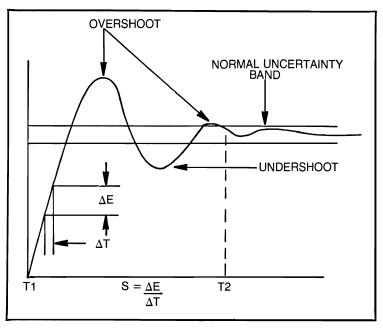

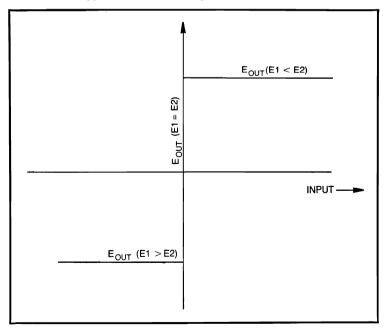

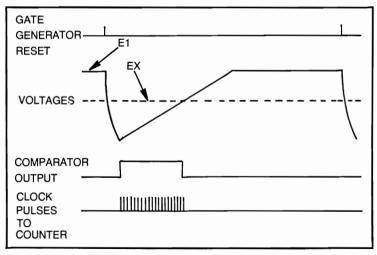

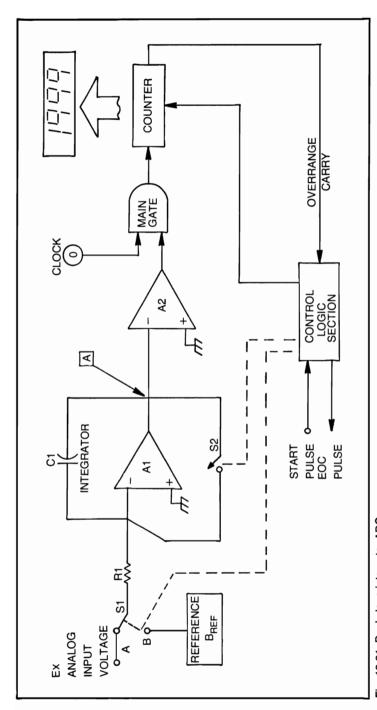

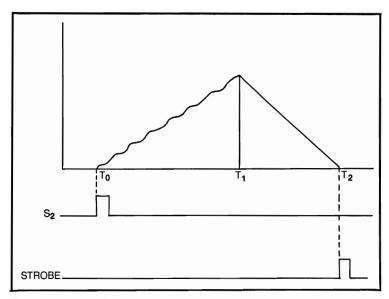

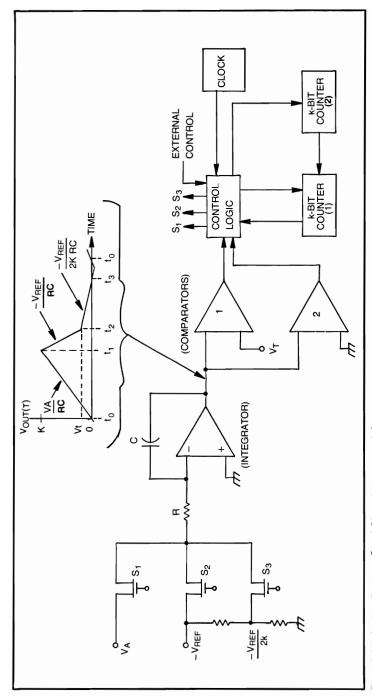

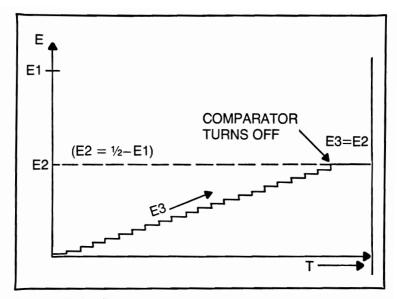

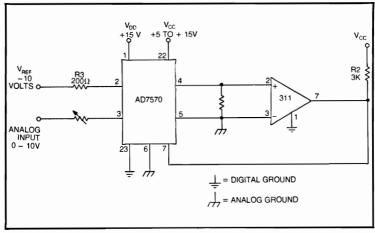

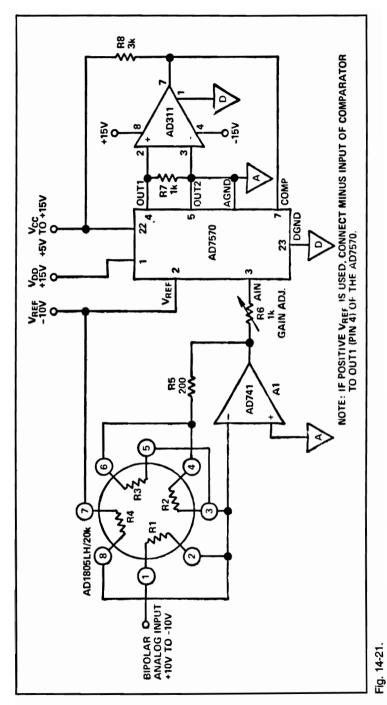

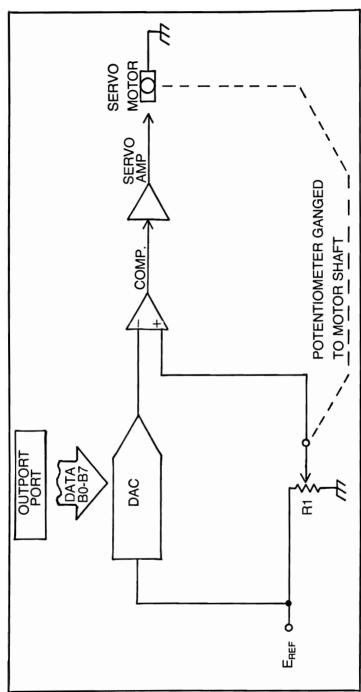

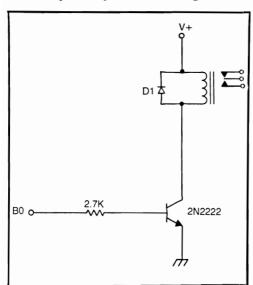

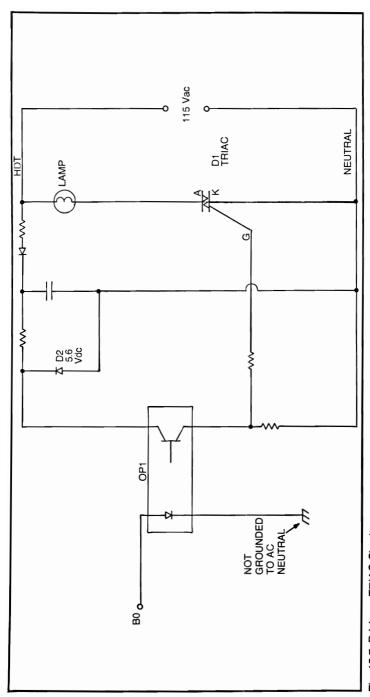

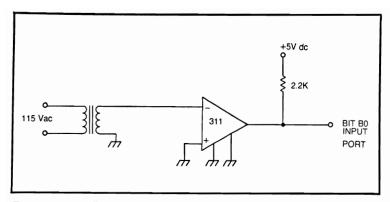

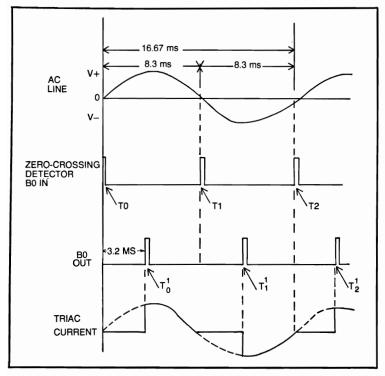

| NMI   | Similar to the INT, except that NMI cannot be turned off                                                          |